## Master 2<sup>nde</sup> année

FPGA et «soft core» RiscV

P-F. Bonnefoi

Réalisation de circuits électroniques contrôlés par

- circuits logiques : maitriser la construction de circuit logique séquentiel ;

- intégrer un circuit digital dans un SoC;

- utiliser ce circuit en programmation «bare metal» en C.

## Moyens pratiques

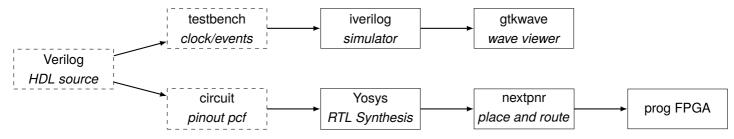

Utilisation de la suite «Open Source» logicielle pour :

- □ utiliser un simulateur de circuit pour vérifier le comportement de son circuit;

- ▶ utiliser un outil de synthèse pour réaliser le circuit physiquement à l'intérieur du FPGA cible ;

- ▷ programmer le FPGA et interagir avec le circuit défini :

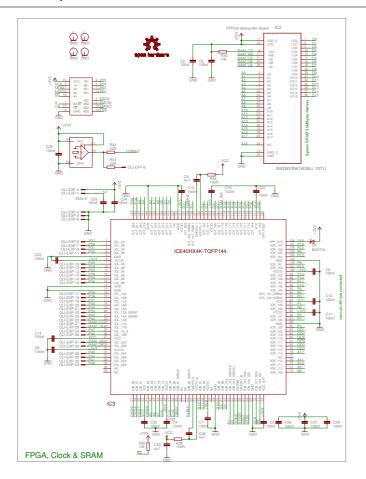

- ♦ carte de développement Black ICE II avec un FPGA Lattice iCE 40 hx8k:

- port série, LEDs, boutons, broches d'E/S, mémoire;

Utilisation du PicoSoc:

- processeur RiscV PicoRV32;

- circuit de chargement de firmware par port série;

- création d'un circuit digitale réalisant un LFSR et intégration dans le SoC;

- ▷ programmation d'un firmware en C utilisant ce LFSR et un mécanisme de «timer».

FPGA et «soft core» – P-FB

Mais un bit, c'est quoi au juste?

## Qu'est-ce qu'un bit, «binary digit»?

Un bit représente un système à deux états possibles :

- □ «allumé», 🗑 ou «éteint», 🗑 ;

- $\square$  «allumé»,  $\square$  ou «éteint»,  $\square$ , d'où le symbole présent sur les interrupteurs poussoir :  $\square$  ou  $\square$

- □ *«Vrai»* ou *«Faux»* :

- $\square$  un **voltage** «bas» t ou un voltage «haut» t (où «v» est le voltage et «t» le temps);

- □ une **magnétisation** de sens nord-sud NS ou de sens sud-nord SN sur un support magnétique ;

- □ la valeur «1» ou la valeur «0».

## Qu'est-ce qu'un bit de mémoire dans un ordinateur?

«Un bit est juste un emplacement de stockage d'électricité:

- ▷ s'il n'y a pas de charge électrique alors le bit est 0;

- ▷ s'il y a une charge électrique alors le bit est 1

La seule chose que l'ordinateur peut mémoriser est si le bit est à 1 ou 0.»

Chaque bit de mémoire correspond à une case dans laquelle on peut stocker un bit de données, soit la valeur 1, soit la valeur 0.

Et un circuit logique, c'est quoi?

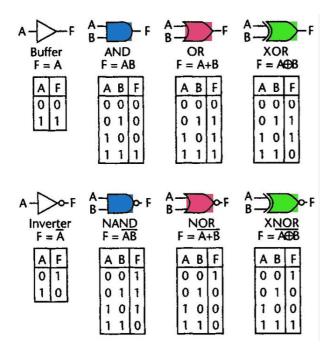

des opérateurs logiques...

et des composants électroniques!

Le «et»: c = a & b ou  $c = a \land b$

Le «non» :

$$b = !a$$

ou  $b = \neg a$

Le «ou» :c = a|b ou  $c = a \lor b$

## Créer des opérations

L'opération

$$x = 1$$

$$x - y$$

$$1 - y$$

L'opération x = 0  $x \longrightarrow 8$

## ⇒ L'opérateur «xor»

Table de vérité du xor

| a | b | Ф |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

On constate que le *xor* est vrai si  $a \neq b$

FPGA et «soft core» – P-FB

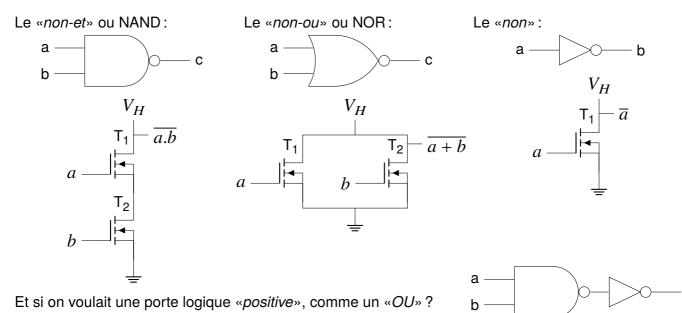

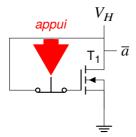

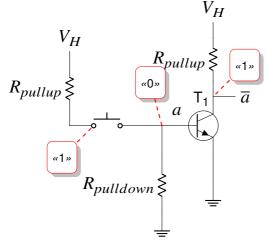

Le **transistor** agit comme un **interrupteur**: le courant peut circuler de la «Source» vers « $le\ Drain$ » uniquement si une tension est présente sur la «Gate»:

## Simuler les portes logiques?

Il est «plus simple» de construire des portes logiques négatives :

Et en vrai?

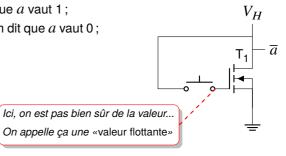

Passer d'un valeur logique à un autre revient à changer le voltage :

$\triangleright 0v$  pour le «0» logique  $\Rightarrow$  ce qui est relié directement au «ground»;

ho  $V_H$  pour le «1» logique  $\Longrightarrow$  ce qui est relié directement à  $V_H$ ;

Exemple sur le «non»:

Si l'entrée a est connectée à

$\, \triangleright \, V_H$  alors on dit que a vaut 1;

ightharpoonup «ground» alors on dit que a vaut 0;

Ce qui donne:

## Et électriquement, ça marche?

Le courant électrique se comporte comme un liquide dont le flot circule du «plus» vers le «moins» :

- le **voltage**, exprimé en volts, qui exprime la «pression» du flot;

- la résistance, exprimée en ohms, qui mesure la résistance opposée à ce flot; On notera également qu'une chute de voltage se produit à la sortie d'une résistance comme pour un liquide où une haute pression en entrée d'un obstacle donne une plus faible pression en sortie

- ☐ l'**intensité**, exprimé en ampères, qui indique la quantité de liquide qui circule. En réalité, le nombre de charges électriques circulant dans le flot (électrons).

En général, c'est l'intensité du courant, son ampérage, qui entraîne des problèmes dans un circuit.

## Loi d'Ohm U = R \* I, ou «volts et résistance crée l'ampérage»

- ⇒l'ampérage >quand la résistance /

Ce qui permet de distinger 3 situations de panne dans un circuit :

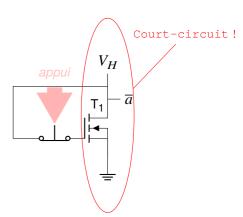

- le **circuit ouvert** où il n'y a pas de circulation ⇒ la **résistance** est infinie et le flot est nul;

- $\triangleright$  le **court-circuit** où le flot va directement vers le «ground» ce qui entraîne trop de flot  $\Longrightarrow$  la **résistance** est très proche de zéro et l'ampérage tend vers l'infini ⇒ les composants brûlent! Ils libèrent la fumée magique qui les faisait fonctionner...

- > pas assez de flot de courant pour que le circuit fonctionne correctement ⇒ la résistance est trop élevée. On remarque que chaque panne est liée à un changement de résistance...

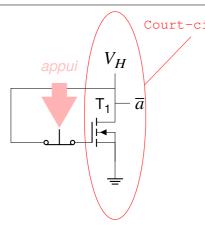

Et finalement?

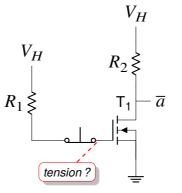

Court-circuit! Il faut ajouter des résistances pour limiter l'intensité du courant, c-à-d son ampérage.

On évite deux court-circuits possibles avec  $R_1$  et  $R_2$ .

Par contre, on ne connait pas la tension à l'entrée de la «gate» du transistor...

## Comment distinguer un «0» et un «1»?

Pour des circuits électroniques «standards» (TTL):

$$\triangleright$$

de  $5v à 2v \implies "1"$ ;

$$\triangleright$$

de  $0,8v \ aov \implies «o»;$

$$ightharpoonup$$

de  $0,9v$  à  $1,9v$   $\Longrightarrow$  «indéfini» ou «flottant»;

## $\Rightarrow "1"$ $2v \qquad \qquad \text{indefini}$ $0, 8v \qquad \qquad \Rightarrow "0"$

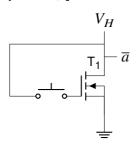

## Autre usage de ces résistances

Elles garantissent une tension:

- ho **Pull up** resistor: garantie une tension proche de  $V_H$ , c-à-d un «1» logique, *ici*,  $R_1$  et  $R_2$ ;

- > **Pull down** resistor: garantie une tension proche de 0, c-à-d un «0» logique, *ici, il n'y en a pas!*

11

On rajoute des résistances de «pull up» pour :

- ▶ forcer une tension interprétable comme un «1» logique;

- éviter un court circuit en cas d'utilisation d'interrupteur pour ouvrir/fermet le circuit;

On rajoute des résistances de «pull down» pour :

- ▶ forcer une tension interprétable comme un «0» logique;

D'où le circuit final:

Et finalement?

Si

$$a=0$$

alors  $\overline{a}=1$

Si

$$a = 1$$

alors  $\overline{a} = 0$

# FPGA et «soft core» - P-FB

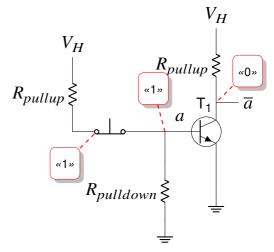

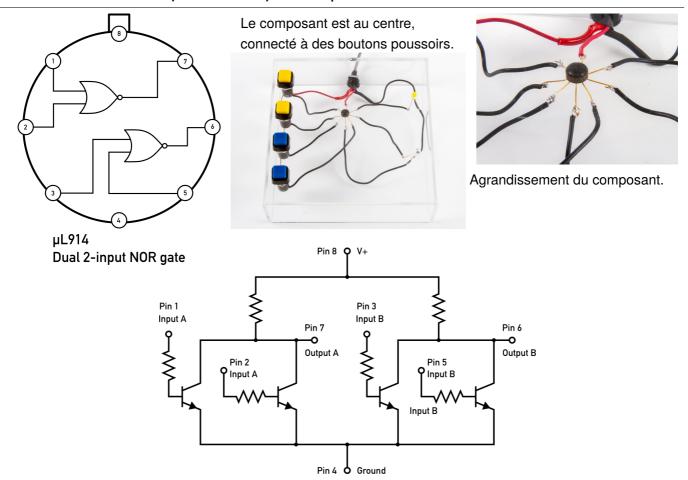

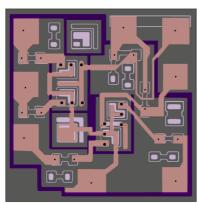

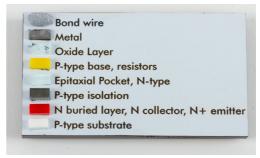

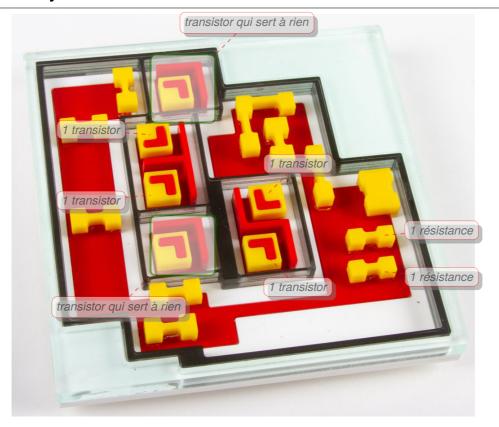

## Et en réalité? Exemple du composant µL914 de la société Fairchild

Et à l'intérieur?

Le composant a été «décapé» : sa coque de protection a été enlevée par abrasion et utilisation d'acides :

Le composant est constitué de différentes couches de matériaux différents, superposées les unes sur les autres. On obtient chaque couche par dépôt de substrat ou par gravure (creusement d'une couche). Et à l'intérieur? 14

Fils de connexion vers l'extérieur:

Couce conductrice:

Les Transistors:

Toutes les couches:

Deux transistors ne servent à rien.

Sans la couche conductrice:

FPGA et «soft core» - P-FB

## Les Transistors:

Les Résistances:

On retrouve chaque transistor et résistance du circuit. Certains transistors ne servent à rien : ils ont été gravés/déposé mais ne sont pas connectés par la couche conductrice.

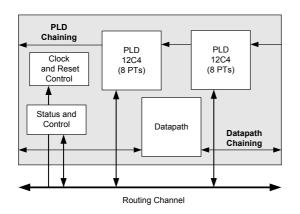

## Mais des circuits logique reconfigurables Ca existe pas déjà avec les CPLDs?

PSoC implements programmable logic through an array of small, fast, low-power digital blocks called Universal Digital Blocks (UDBs). PSoC devices have as many as 24 UDBs. A UDB consists of two small programmable logic devices (PLDs), a datapath module, and status and control logic.

**UDB**

PLD

### D'après la documentation

PSoC PLDs, like most standard PLDs, consist of an AND array followed by an OR array, both of which are programmable. There are **12 inputs** which feed across **eight product terms** (PTs) in the AND array. In each PT, either the true (T) or complement (C) of the input can be selected. The **outputs of the PTs** are inputs into the **OR array**.

The outputs of the OR gates are fed to **macrocells** (MC). Macrocells are **flip-flops** with additional combinatorial logic.

# FPGA et «soft core» - P-FB

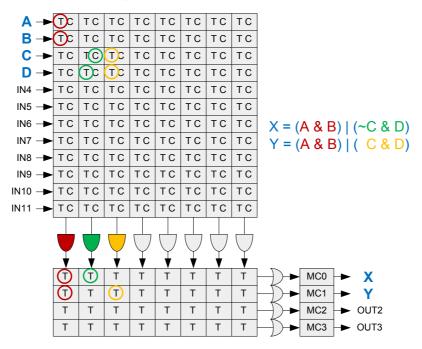

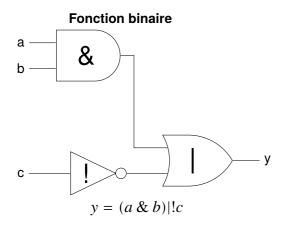

## Exemple de circuit simulant une fonction logique

## D'après la documentation

PSoC PLDs, like most standard PLDs, consist of an AND array followed by an OR array, both of which are programmable. There are **12 inputs** which feed across **eight product terms** (PTs) in the AND array. In each PT, either the true (T) or complement (C) of the input can be selected. The **outputs of the PTs** are inputs into the **OR array**.

The outputs of the OR gates are fed to **macrocells** (MC). Macrocells are **flip-flops** with additional combinatorial logic.

Mais comment les bits sont mémorisés?

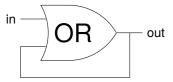

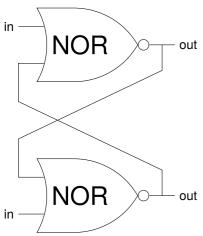

## Que se passe-t-il si on branche la sortie en entrée d'une porte logique?

Ici, que se passe-t-il?

- > au début on peut imaginer que :

- ♦ l'entrée «in» est à zéro;

- ♦ la sortie «out» est à zéro;

- ▶ Mais dès que l'entrée «in» passe à un alors la sortie reste bloquée à un!

| a | b | OR |

|---|---|----|

| ) | 0 | 0  |

| ) | 1 | 1  |

| 1 | 0 | 1  |

| 1 | 1 | 1  |

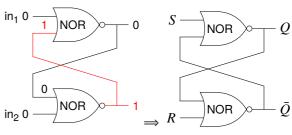

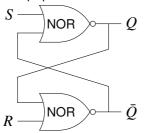

## Comment faire pour «l'éteindre» ?

| a | b | NOR |

|---|---|-----|

| ) | 0 | 1   |

| ) | 1 | 0   |

| 1 | 0 | 0   |

| 1 | 1 | 0   |

# FPGA et «soft core» - P-FB

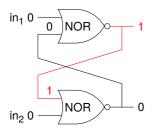

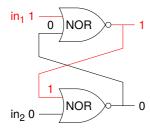

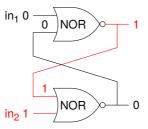

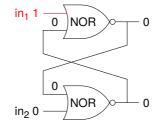

## À l'allumage du circuit que se passe-t-il?

**1** À l'allumage, les entrées sont à zéro :⇒ on obtient :

- 3 Si on mets l'entrée «in<sub>1</sub> à un» :

- ⇒on obtient :

- 2 Si on mets l'entrée «in<sub>2</sub>» à un :

- ⇒l'état du circuit ne change pas :

- 4 Si on mets l'entrée «in<sub>1</sub>» à un :

- ⇒l'état du circuit change vers :

- a b NOR

0 0 1

0 1 0

1 0 0

1 1 0

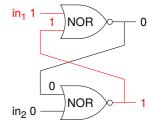

- Si on mets l'entrée «in₁» à un :

⇒ l'état du circuit se stabilise sur :

- ⇒le circuit ne change pas;

- ⇒on est dans l'image inversée de l'état précédent où l'état ne changeait plus...

- ⇒ On vient de construire une «S-R Latch», une «set/reset» latch!: un bouton «set» et l'autre «reset»

- ⇒On vient de mémoriser un état!

# FPGA et «soft core» - P-FB

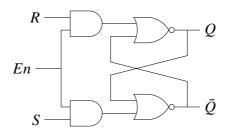

## Améliorer le circuit ? Ajouter une entrée «enable»

On ajoute le «enable» qui permet d'activer ou non la SR-latch :

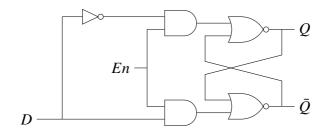

Si on va plus loin: mémorisation d'un bit «à la demande»

## À chaque fois que:

- ightharpoonup l'entrée «enable» est active : la sortie «Q» reproduit la valeur de l'entrée «D» ;

- $\,dash$  l'entrée «enable» est inactive : la sortie «Q» conserve sa valeur quelque soit la valeur de D ;

On «copie» la valeur de D en activant le «enable».

⇒On peut mémoriser un bit d'information à la demande!

L'horloge 23

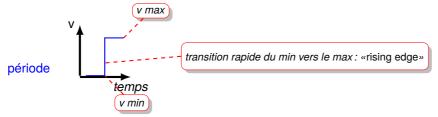

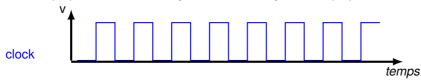

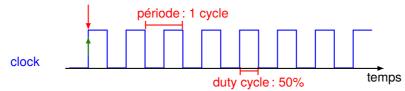

## Qu'est-ce que l'horloge?

### Un signal électrique:

- □ une variation de tension entre 0v et 3,3v ou 5v (en fonction des micro-contrôleurs par exemple);

- > périodique : la période est une portion du signal qui se reproduit indéfiniement :

où le temps passé avec le voltage maximal est égal au temps passé avec le voltage minimal (duty cycle de 50%).

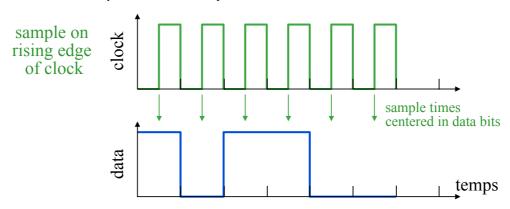

Front montant ou «rising edge»

- ▷ en résumé :

- ⇒ servir de **référence globale** dans le circuit;

- ⇒ synchroniser les différentes parties de ce circuit.

En général, on utilise le front montant ou «rising edge» pour effectuer cette **synchronisation**.

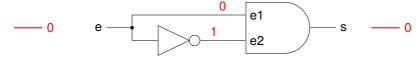

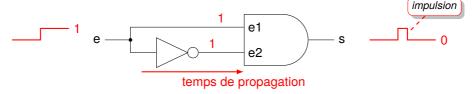

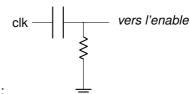

## Introduction d'un délai : détection du front montant, «rising edge», de l'horloge

La traversée de la porte logique «NOT» introduit un délai qui permet au «ET» de sortir un 1 pendant un court instant.

Pendant un court instant, les entrées «e1» et «e2» sont vraies ⇒ une impulsion en sortie.

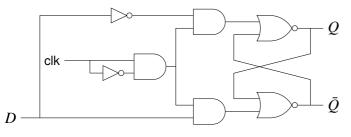

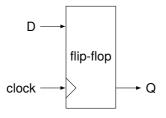

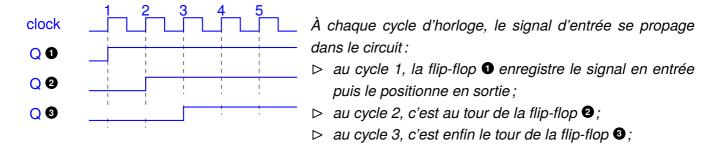

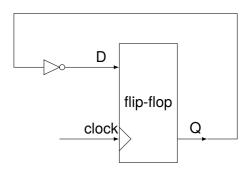

## Combinaison avec le circuit de mémorisation à la demande : la «D flipflop»

Si on utilise l'horloge pour l'entrée «*enable*» on obtient une **mémoire synchronisée** sur l'horloge!

$\Rightarrow$  la «D-flipflop»

La valeur D est mémorisée/accessible au moment où l'horloge change  $\Longrightarrow$  on peut synchroniser différents circuits entre eux.

On peut également utiliser un condensateur pour générer l'impulsion :

25

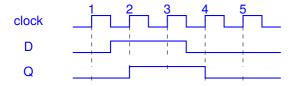

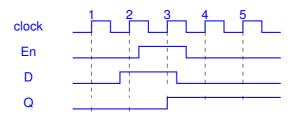

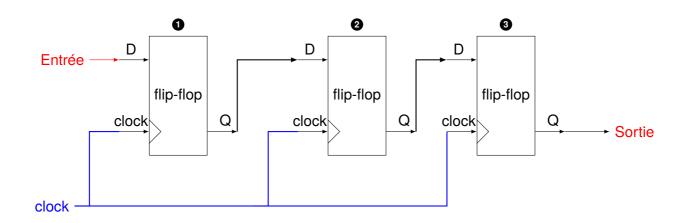

## La D flip-flop

- ▷ le signal «D» devient actif, il vaut «1», entre les cycles d'horloges 1 et 2, c-à-d avant le front montant de 2

⇒ il est ignoré par la flip-flop

⇒ le signal «Q» est inactif, il vaut «0»;

- ▷ lors du front montant 2, la flip-flop enregistre, «*register*», le changement du signal «D»  $\Rightarrow$  «Q» devient actif.

De même, lorsque le signal «*D*» passe à 0, la flip-flop ne l'enregistrera qu'au prochain front montant en 4.

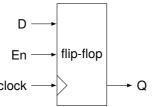

On ajoute une entrée «Enable» à la D flip-flop:

▷ lorsque le signal «En» n'est pas actif⇒pas de modification de Q. C'est seulent en 3 que Q enregistre D.

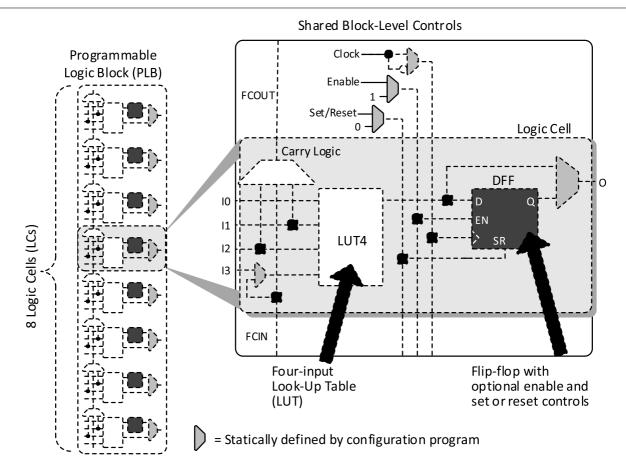

Ce sont ces D-Flip-flop qui sont intégrées dans les FPGAs : elles enregistrent D aussi longtemps que voulu.

Et les circuits logique dans tout ça?

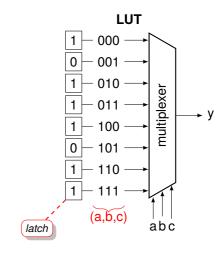

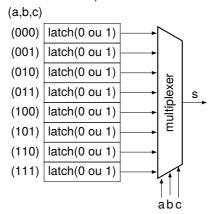

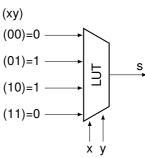

Une fonction binaire de *n* entrées vers un bit en sortie peut être simulée par une LUT:

- hd pour chaque combinaison des variables d'entrées (a,b,c), une valeur de sortie y est **mémorisée** :

- la fonction binaire n'est pas implémentée sous forme de portes logiques;

- le temps de propagation nécessaire à la traversée de chaque portee logique en série est minimisé;

- la sélection de la valeur de sortie par rapport aux valeurs en entrée est faite par un multiplexeur :

- suivant le nombre d'entrées du multiplexeur, il peut être nécessaire d'en combiner plusieurs si on a besoin de plus d'arguments ou de plus de bits en sortie

de la BRAM, «block ram» peut être utilisée en remplacement.

- ightharpoonup la configuration de chaque valeur de sortie y dans le multiplexeur est :

- définie dans le «bitfile» lors de la synthèse du design;

- mémorisée dans un latch lors de la programmation du FPGA.

# FPGA et «soft core» – P-FB

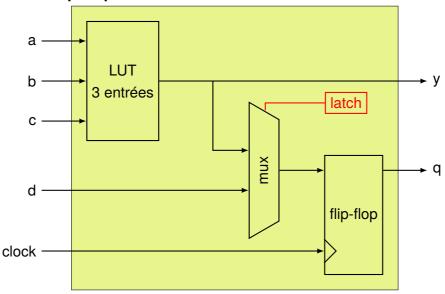

## Associer une LUT et une Flip-Flop

### La sortie:

- «y» sert au circuit logique séquentiel;

- □ «q» sert au circuit logique combinatoire.

## Le «latch»:

- sert à sélectionner la sortie de la LUT ou celle de la Flip-Flop;

- ▷ est configuré dans le «bitfile» lors de la programmation du FPGA.

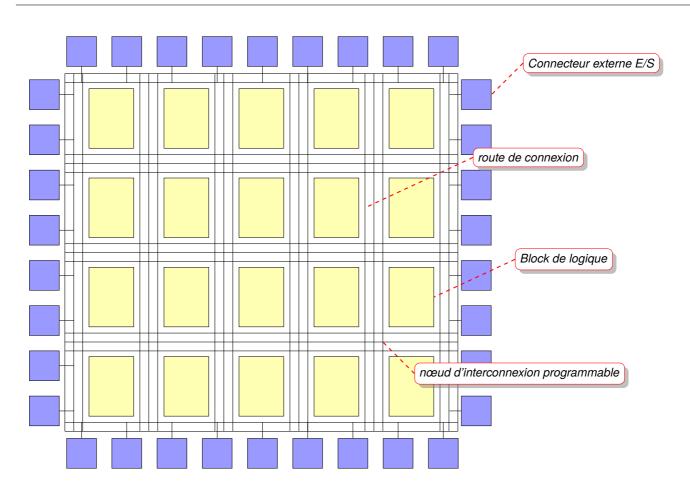

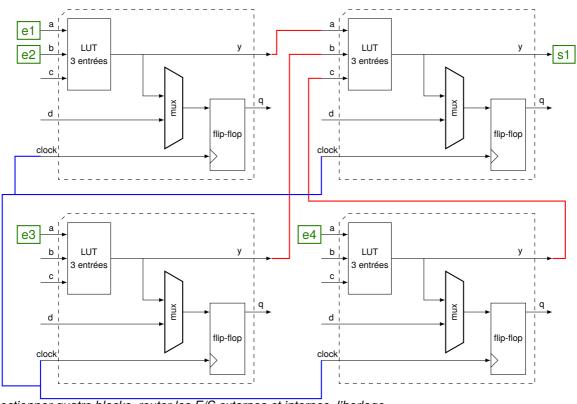

## Schéma fonctionnel d'un FPGA: milliers de blocs logiques interconnectés29

-PGA et «soft core» - P-FB

Donc, programmer un FPGA:

c'est choisir une interconnexion de blocs logiques?

Sauver cette configuration dans un fichier «bitstream»

Et c'est tout?

## Configuration de la LUT dans le «bit stream»

- $\triangleright$  chaque combinaison de (a,b,c) est associée à un bit configuré par la valeur contenue dans une «*latch*»;

- ⊳ la configuration de toutes les «latches» d'un multiplexeur est faite dans le fichier de configuration du FGPA : le «bit stream» ;

Des multiplexeurs peuvent être utilisés pour servir de ROM, «Read Only Memory», où la configuration d'un bit peut être consultée mais pas modifiée pendant l'utilisation du FPGA.

En particulier, on peut grouper plusieurs LUTs:

- $\triangleright$  pour stocker des «données» sur plusieurs bits : même sélection par (a,b,c) mais pour un bit à la fois : 8 muliplexeurs par exemple pour stocker un octet.

- ▷ en cascade pour augmenter le nombre de sélecteur :

- une LUT à 3 entrées utilisée sur une seule entrée pour la sélection de deux autres LUTs à 3 entrées : on passe à une LUT à 4 entrées.

- ⇒Le nombre d'entrées pour une LUT doit être choisie de manière optimale.

- ⇒ Dépend du choix du constructeur : pour le iCE40 de Lattice, ce sont des LUTs de 4 entrées qui ont été choisies.

## Mais...

il y aurait pas des problèmes tout de même?

## Les problèmes de temporisation induites par l'interconnexion de blocs logiques 34

Les processus de placement et routage doivent garantir que :

- ▷ le circuit est viable :

- ⇒les composants sont exploités à une vitesse qu'ils peuvent supporter sans erreur.

Une **évaluation** est faite par l'outil de *«pnr»*, pour déterminer le temps maximal de propagation, c-à-d le temps pour un signal d'arriver de la source à sa destination.

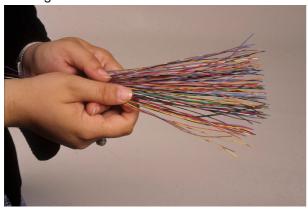

Un signal voyage en une *nanoseconde*,  $10^{-9}$  ou 1GHz, sur une distance de 30cm environ.

Photo ci-contre de l'illustration d'une «nanoseconde» pat Grace Hopper.

> les routes mise en place peuvent être assez longues ⇒ le temps de propagation à travers ces routes augmente;

- - > LUT;

- flip-flop;

- ♦ BRAM, «Bloc RAM»

. .

Les processus de placement et routage, «pnr», doivent tenir de ces contraintes de propagation :

⇒ils recherchent le **meilleur placement possible** qui **minimise le temps de propagation** lié au routage!

⇒Il faut **3 cycles d'horloge** pour propager le signal à travers le circuit.

Ok, mais au niveau électronique il y aurait pas aussi des soucis?

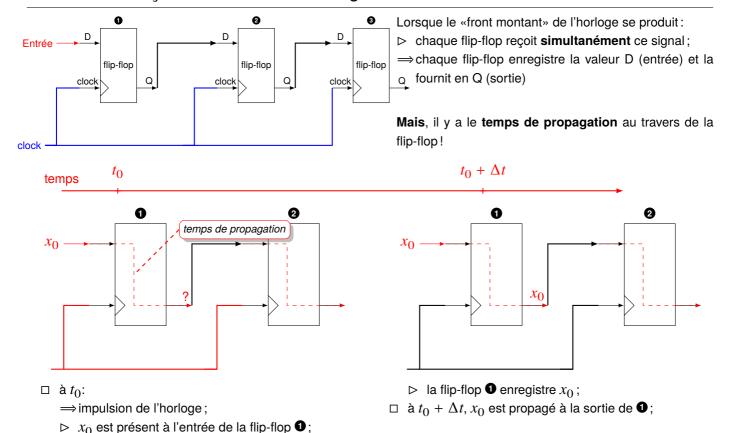

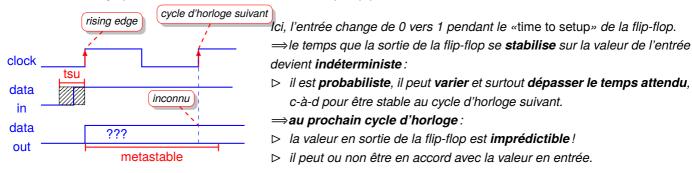

### Contraintes liées aux flip-flops

- «th», «Time to Hold»: la durée pendant laquelle l'entrée doit rester stable après le front montant de l'horloge pour que la flip-flop puisse conserver correctement sa valeur en sortie jusqu'au prochain cycle d'horloge.

### ATTENTION: la flip flop peut être dans un état inconnu au prochain cycle d'horloge

Si l'entrée change pendant le «tsu» ou le «th» alors la flip-flop peut se retrouver dans un état «metastable» :

⇒La sortie de la flip-flop au cycle d'horloge suivant est instable : soit 0, soit 1 ou «une valeur» intermédiaire (elle atteindra la bonne valeur qu'après le cycle d'horloge attendu).

### Documentation du Lattice ICE40 LP/HX family

|                 |                                          |            |       |   | _  |

|-----------------|------------------------------------------|------------|-------|---|----|

| t <sub>SU</sub> | Clock to Data Setup - PIO Input Register | iCE40LP384 | -0.08 | - | ns |

|                 |                                          | iCE40LP640 | -0.33 | _ | ns |

|                 |                                          | iCE40LP1K  | -0.33 | _ | ns |

|                 |                                          | iCE40LP4K  | -0.63 | _ | ns |

|                 |                                          | iCE40LP8K  | -0.63 | _ | ns |

| t <sub>H</sub>  | Clock to Data Hold - PIO Input Register  | iCE40LP384 | 1.99  | _ | ns |

|                 |                                          | iCE40LP640 | 2.81  | _ | ns |

© 2011-2023 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

32 FPGA-DS-02029-4.1

iCE40 LP/HX Family Data Sheet

| Parameter                                                                    | Description | Device    | Min. | Max. | Units |

|------------------------------------------------------------------------------|-------------|-----------|------|------|-------|

|                                                                              |             | iCE40LP1K | 2.81 | _    | ns    |

|                                                                              |             | iCE40LP4K | 3.48 | _    | ns    |

|                                                                              |             | iCE40LP8K | 3.48 | _    | ns    |

| General I/O Pin Parameters (Using Global Buffer Clock with PLL) <sup>3</sup> |             |           |      |      |       |

Ici, on voit que le  $t_{su}$  vaut -0,63ns, cela veut dire que le signal peut arriver un peu après le «cycle d'horloge» et être encore correctement enregistré par la flip-flop.

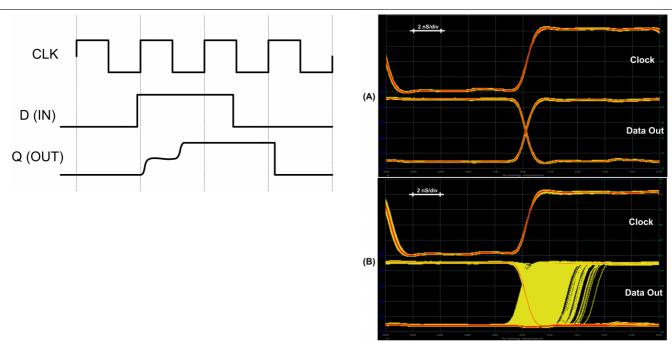

### Sur cette mesure:

- > on superpose la trace de centaines modification de la valeur de sortie de la flip-flop;

- $\triangleright$  en (A), la transition de 0 à 1 ou de 1 à 0 se passe correctement au cycle d'horloge si on respecte le  $t_{su}$  et le  $t_h$ ;

- $\triangleright$  en cas de non respect du  $t_{su}$  ou  $t_h$ , on subit de la «méta-stabilité» et on voit qu'il faut jusqu'à 5ns pour que la valeur de sortie de la flip-flop atteigne une valeur stable!

https://colinoflynn.com/2020/12/experimenting-with-metastability-and-multiple-clocks-on-fpgas/

Du coup, pas de solution possible?

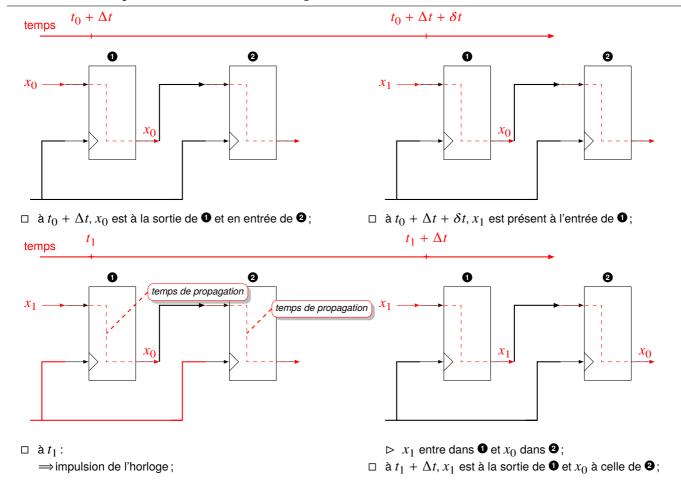

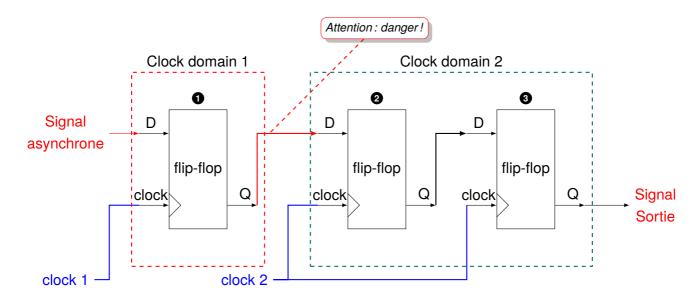

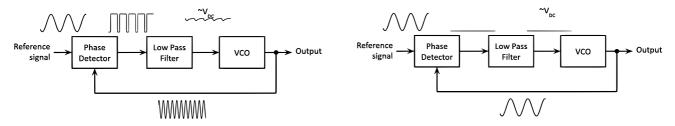

### lci:

- □ le «clock domain 1» est synchronisé sur l'horloge «clock 1»;

- le «clock domain 2» est synchronisé sur l'horloge «clock 2».

- ▷ il y a un risque de méta-stabilité dans la flip-flop ①;

- ⇒on utilise les flip-flop 2 et 9 pour synchroniser dans le «domain clock 2».

- ⇒ les flip-flps 2 et 3 sont appelées un «synchronizer».

### Donc les flip-flops induisent des contraintes sur notre FPGA?

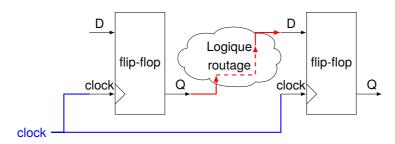

### Exemple de circuit

- □ le circuit contient deux flips-flops avec un signal circulant de la sortie de la première vers l'entrée de la seconde ;

- □ ce signal doit traverser un nuage de route/LUTs où va se produire des délais de propagation : plus le nuage contient de LUTs/route à traverser, ✓ plus le délai de propagation ✓

- les deux flip-flops sont pilotées par la même horloge;

- $\square$  si la première flip-flop enregistre son entrée D et la propage vers sa sortie Q:

- ⇒le signal dispose d'un seul cycle d'horloge pour se propager de la première flip-flop vers la seconde ;

- □ si le signal arrive à temps, alors le circuit fonctionne ;

- □ si le routage et les éléments logiques à traverser induisent un **délai de propagation trop important**⇒il va y avoir un «*timing error*» car le design est incapable d'atteindre les objectifs fixés.

- ⇒ C'est à l'outil de «pnr» d'analyser chaque chemin et de remonter à l'utilisateur quel est le pire des chemins en terme de délai de propagation.

Le circuit a moins d'un cycle d'horloge à cause du «tsu» de la seconde flip-flop!

$$min(t_{clock}) = t_{su} + t_p$$

- ⇒ Période d'horloge minimale permettant au circuit de fonctionner sans erreurs de temporisations.

- ⇒ fréquence d'horloge maximale pour laquelle le circuit fonctionne correctement.

### Conception de circuits logiques avec Verilog

- ▷ langage de **description matériel**, HDL, «*Hadware Definition Language*»;

- □ utilise une syntaxe similaire au C: opérateurs logiques, contrôle de flow (if/else, case), sensible à la casse, préprocesseur, etc.;

- ▷ «décrit» le comportement, «behavior», du circuit attendu :

- ♦ le circuit est simulé grâce aux composants disponibles : flip-flops, LUT, RAM, DSP, etc.;

- les composants utilisés sont ensuite sélectionnés et reliés entre eux: «place and route»;

- un calcul de faisabilité est réalisé sur la proposition: contraintes dues aux temps de propagation des chemins définis lors du placement/routage, limite des fréquences utilisables, etc;

- si les contraintes sont :

- \* respectées: le placement/routage est accepté, une solution est atteinte;

- \* non respectées: on essaye un nouveau placement/routage pour obtenir une nouvelle proposition;

### > il contient:

- des parties «synthétisables»: pouvant donner lieu à un circuit physique;

- des parties non synthétisable: affichage, delais, par exemple pour faire des simulations, tests ou déboguages;

- ▷ Seul le résultat synthétisable peut être traduit en :

- ♦ FPGA, «Field Programmable Gate Array»;

- ASIC, «Application-Specific Integrated Circuit»;

- ▷ un concurrent: VHDL, «VHSIC Hardware Description Language» avec VHSIC signifiant, «Very High Speed Integrated Circuit»;

### Développement pour FPGA: la suite «Open Source»

celui qu'on va utiliser

### ▷ yosys:

- ☐ framework for RTL, «Register-Transfer Level» synthesis tools; It currently has

- extensive Verilog-2005 support;

- □ basic set of synthesis algorithms for various application domains.

### > nextpnr:

- □ vendor neutral, timing driven, FOSS FPGA place and route tool.

- □ Lattice iCE40 devices supported by Project IceStorm

- □ Lattice ECP5 devices supported by Project Trellis

- □ Lattice Nexus devices supported by Project Oxide

- □ Gowin LittleBee devices supported by Project Apicula

- ☐ (experimental) Cyclone V devices supported by Mistral

- □ (experimental) Lattice MachXO2 devices supported by Project Trellis

### icarus verilog, «iverilog»:

simulator.

### gtkwave:

wave viewer, scriptable with TCL.

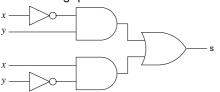

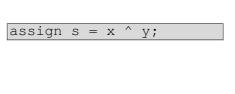

Le circuit logique du «xor»:

Son comportement exprimé en Verilog: Sa simulation en FPGA:

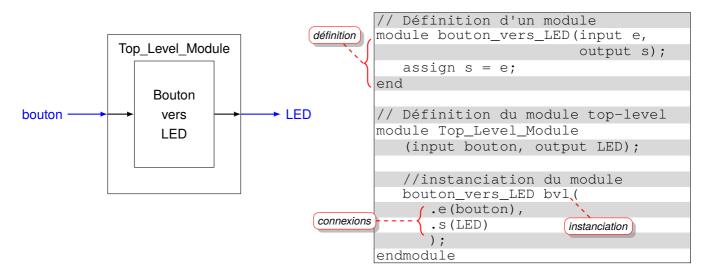

### La notion de module

- □ le **module** est l'élément de base du circuit : il fournit **abstraction** et **encapsulation** ;

- un module doit être écrit dans un fichier verilog (extension «.v») dont le nom correspond à celui du module ;

- □ un module est constitué de :

- une liste de «ports»;

- le code verilog implémentant les fonctionnalités désirées;

- □ les «ports» permettent les **connexions** entre un module et son environnement:

- chaque «port» possède un nom et un type: input, output ou inout;

- les «ports» sont déclarés dans la partie «port declaration» du module :

```

module example_design (input entree, output sortie);

assign sortie = entree;

endmodule

les ports du module

```

### Le module de «Top Level»

- □ tous les circuits complets ont un module «top-level» qui est au sommet de la hiérarchie des différents modules ;

- □ le module «top-level» définit les E/S pour l'intégralité du système digital;

- tous les modules du circuit complet sont instanciés à l'intérieur de ce module «top-level»:

- ▶ L'instanciation du module «bouton\_vers\_led» définit le module appelé «bvl»;

- ▶ Les connexions «.e (bouton) » et «.s (LED) » connectent les E/S du module «bvl» à celles du module top-level.

«Wires» ou «fils»

- > correspondent à des fils de connexion : transmettre des valeurs entre entrées et sorties ;

```

wire a;

wire b;

```

```

wire [7:0] d; // 8bits

wire [31:0] e; // 32 bits

```

Sont définis en vecteur multi-bits avec la syntaxe [MSB bit index : LSB bit index] avant le nom du signal pour définir sa taille en bits :

```

module traitement_sur_deux_bits ( input [1:0] x, output [1:0] y);

wire [1:0] valeur_temporaire;

...

endmodule

```

- ⊳ lorsque l'on connecte des entrées multi-bits vers des sorties multi-bits, le nombre de bits doit correspondre!

- > un fil, «wire», peut être affecté à des équations logiques, d'autres fils ou des opérations réalisées sur ses fils :

- ♦ on utilise l'instruction «assign»:

- \* l'argument de gauche de «assign» doit être un «wire» mais ne peut pas être un «input wire»;

- \* l'argument de droite de «assign» peut être n'importe quelle expression consituées d'opérateurs de Verilog et de «wires»:

```

module connecter(input a, output b);

assign a = !b;

endmodule

```

### Et en terme de placement/routage ca donne quoi?

### Réaliser un circuit dans un FPGA C'est résoudre un problème de contraintes

### Retournons sur Verilog

Les opérateurs 55

| Opérateur       | Symbol | Opération               |  |

|-----------------|--------|-------------------------|--|

| aithnéidue      | +      | addition                |  |

| ithnette        | -      | soustraction            |  |

| atte            | *      | multiplication          |  |

|                 | /      | division                |  |

|                 | %      | module                  |  |

| logique         | !      | non logique             |  |

|                 | &&     | et logique              |  |

|                 | II     | ou logique              |  |

| relationnel     | >      | plus grand que          |  |

| elatio,         | <      | moins grand que         |  |

| ζ-              | >=     | plus grand que ou égal  |  |

|                 | <=     | moins grand que ou égal |  |

| boalite         | ==     | égal                    |  |

| 8 <sub>02</sub> | !=     | différent               |  |

| Opérateur        | Symbol | Opération                      |  |

|------------------|--------|--------------------------------|--|

| dit a bit        | ~      | négation                       |  |

| Ojt.             | &      | et                             |  |

|                  |        | ou                             |  |

|                  | ۸      | xor                            |  |

| 98CA18OR         | <<     | décalage à gauche logique      |  |

| 9/scg.           | >>     | décalage à droite logique      |  |

|                  | <<<    | décalage à gauche arithmétique |  |

|                  | >>>    | décalage à gauche arithmétique |  |

| concaténation    | {}     | grouper des bits               |  |

| duplication      | {{}}   | dupliquer des bits             |  |

| indexer/découper |        | sélectionner des bits          |  |

### **Exemples**

```

wire [7:0] a;

wire [31:0] b;

wire [31:0] c;

assign c = {a, b[23:0]};// concaténation et découpage

assign c = { 32{a[5]} };// duplication et indexage

```

```

wire operande1 [31:0];

wire operande2 [31:0];

wire resultat [31:0];

assign resultat = operande1 + operande2;

```

### Opérateur ternaire : «if-else» avec une instruction «assign»

```

assign sortie = a > 10 ? 10 : a ; // affecte 10 si <math>a > 10, sinon affecte a

```

### Entrée des valeurs

où la base peut être :

□ d : décimal ;

□ o : octal ;

Attention

h: hexadécimal;

Il est important de faire correspondre le nombre de bits des opérateurs et des connexions entre modules!

b: binaire.

[nbre de bit]'[base][valeur]

### **Exemples**

| 2'd 2        | la valeur sur 1 sur 2 bits: 10 |  |  |

|--------------|--------------------------------|--|--|

| 16'h abcd    | la valeur Oxabcd en hexadécima |  |  |

| 8'b 10001100 | la valeur 0b10001100           |  |  |

### Registre

permettent de mémoriser un état qui peut changer :

syntaxe de 2001 vs syntaxe de 1995

reg x; reg [31:0] y; // ou reg y [31:0]

différent du «wire» qui sert à connecter ou à fixer une valeur :

wire [1:0] c = 2'b 01;

### Bloc de logique combinatoire, «Combinational Logic Blocks»: le «always @(\*)»

```

reg x;

reg y;

la liste de sensibilité

always @(*) begin

x = ~y;

end

```

La liste de «sensibilité» ou «sensitivity list» est la liste des signaux à surveiller et dont la modification entraîne la ré-évaluation du bloc.

lci, on mets (\*), ce qui veut dire que le bloc est recalculé pour toute modification des signaux qu'il utilise en entrée, c-à-d ici y.

### L'instruction conditionnelle «if-else»

```

wire w;

wire x;

wire y;

reg [1:0] z;

always @(*) begin

if (x) begin

z[0] = x;

z[1] = y;

end

else begin

z[0] = y;

z[1] = x;

end

end

```

- ▷ l'utilisation de «if-else» entraîne la génération de multiplexeurs en hardware;

- ⊳ si plusieurs opérations sont nécessaires, il faut les encapsuler dans un «begin-end»;

### Attention

Il est important de traiter toutes les valeurs de la condition.

```

reg [1:0] x;

reg [1:0] y;

always @(*) begin

case(x)

0: y = 2'd 2;

1: y = 2'd 3;

2: y = 2'd 1;

default: y = 2'd 0;

endcase

end

```

Ce code va générer plusieurs multiplexeurs pour le mettre en œuvre en hardware.

Attention

Il est important de mettre un «default».

### Attention à ne pas générer des «latches» au lieu de «flip-flops»

Un latch ne dépend pas de l'horloge pour enregistrer sa valeur ⇒il peut être **imprévisible** et doit être éviter.

Code pouvant générer un «latch»:

```

wire [1:0] x;

reg [1:0] y;

always @(*) begin

if(x == 2'b10) begin

y = 2'd3;

end else if(x == 2'b11) begin

y = 2'd2;

end

end

```

*Ici, on affecte pas de valeurs au registre y quelles que soient les valeurs de x.*

Code ne générant pas de «latch»:

lci, il y a une valeur par défaut.

### Génération involontaire de «latches»

| entree A | entree B | sortie Q  |

|----------|----------|-----------|

| 0        | 0        | 0         |

| 0        | 1        | 1         |

| 1        | 0        | 1         |

| 1        | 1        | undefined |

lci.

- ▷ la sortie vaut zéro si les deux entrées valent zéro ;

- ▷ la sortie vaut un si les deux entrées sont différentes;

Mais que se passe-t-il si les deux entrées valent un?

### L'outil de programmation FPGA va conclure que dans ce cas là, la sortie doit conserver son état précédent!

⇒ une «latch» va être générer pour mémoriser cet état sans utiliser l'horloge.

Le comportement sera alors le suivant :

- ▷ si la valeur de la sortie est 0 et que les deux entrées sont à 1 alors la sortie reste à 1;

- ▷ si la valeur de la sortie est 1 et que les deux entrées sont à 1 alors la sortie reste à 1;

### Attention

Dans un «case» ou une succession de «if-else» il est nécessaire de traiter toutes les combinaisons possibles des conditions et/ou d'utiliser une valeur par défaut.

### Les blocs de logiques séquentielles

- utilisent un identifiant spécial dans leur liste de sensibilitée : «posedge» qui signifie «front montant»

```

reg [1:0] x;

always @(posedge clk) begin

x \le x + 1;

end

```

lci, on incrémente x tous les cycles d'horloge.

### Affectation bloquante et non bloquante

Verilog dispose de deux opérateurs d'affectation :

- > <=: affectation non bloquante = réservé pour les blocs de logique séquentielle ;

- «Non bloquant» signifie qu'il n'empêche pas les autres affectations d'avoir lieu en même temps.

- ⇒ toutes les affectations ont lieu en même temps et seront valides au prochain cycle d'horloge.

- > = : affectation bloquante ⇒ réservé pour les blocs de logique combinatoire.

- «Bloquant» signifie que les affectations suivantes auront lieu uniquement après celle-ci.

- ⇒les affectations sont réalisées dans l'ordre d'écriture dans le source Verilog.

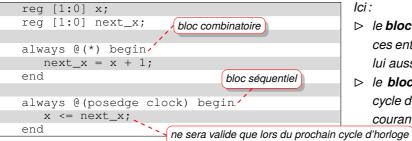

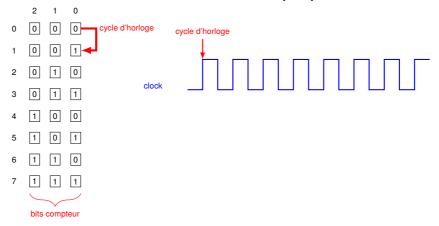

### Exemple: un compteur qui s'incrémente à chaque cycle d'horloge

lci:

- ▷ le bloc combinatoire réagit à chaque modification de ces entrées : dès que x est modifié alors next x est lui aussi modifié (après que l'addition soit finie):

- ▷ le bloc séquentiel ne réagit que lors d'un nouveau cycle d'horloge : à ce moment là il enregistre la valeur courante de next\_x dans x

### Utilisation de https://www.edaplayground.com/

### testbench.sv

```

module testbench();

reg clock;

initial begin

clock = 1'b1;

forever #5 clock = ~clock;

end

compteur dut(

.clock(clock)

);

initial begin

$dumpfile("dump.vcd"); $dumpvars;

#100 $finish;

end

endmodule

```

### design.sv

```

module compteur(input clock);

reg [1:0] x = 0;

reg [1:0] next_x = 0;

always @(*) begin

next_x = x + 1;

end

always @(posedge clock) begin

x <= next_x;

end

endmodule</pre>

```

Brought to you by A DOULOS (http://www.doulos.com)

### Utilisation de https://www.edaplayground.com/

### testbench.sv

```

module testbench();

reg clock;

initial begin

clock = 1'b1;

forever #5 clock = ~clock;

end

compteur dut(

.clock(clock)

);

initial begin

$dumpfile("dump.vcd"); $dumpvars;

#100 $finish;

end

endmodule

```

### design.sv

on supprime la partie combinatoire.

Brought to you by DOULOS (http://www.doulos.com)

### et la version précédente :

Brought to you by A DOULOS (http://www.doulos.com)

### Utilisation de https://www.edaplayground.com/

### testbench.sv

# module testbench(); reg clock; initial begin clock = 1'b1; forever #5 clock = ~clock; end compteur dut( .clock(clock) ); initial begin \$dumpfile("dump.vcd"); \$dumpvars; #100 \$finish; end endmodule

### design.sv

```

module yop(input clock);

reg [1:0] x = 0;

always @(posedge clock) begin

x <= x + 1;

end

endmodule</pre>

```

on supprime l'utilisation de next\_x.

Brought to you by A DOULOS (http://www.doulos.com)

### et la version 1:

Brought to you by A DOULOS (http://www.doulos.com)

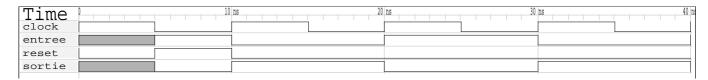

```

module oscillator

(input clock, input reset, output reg sortie);

wire entree;

assign entree = ~sortie;

always @(posedge clock or posedge reset) begin

if (reset)

sortie <= 0;

else

sortie <= entree;

end

endmodule</pre>

```

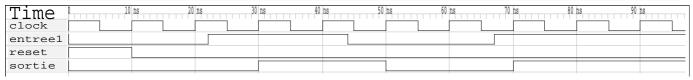

### La flip-flop change de valeur à chaque cycle d'horloge :

Ceci est la sortie de gtkwave.

```

`include "oscillator.v"

`timescale 1ns / 1ps

module tb ();

wire sortie;

reg clock;

rea reset;

oscillator dut(.clock(clock),

.reset(reset), .sortie(sortie));

initial begin

clock = 1;

forever #5 clock <= ~clock;

end

initial begin

reset = 0;

#5 \text{ reset} = 1;

#5 \text{ reset} = 0;

end

initial begin

$monitor("time=%3d, sortie=%b", $time, sortie);

$dumpfile("oscillator.vcd");

$dumpvars(0, tb);

#40 $finish ;

end

endmodule

```

À chaque cycle d'horloge, la flip-flop change de valeur:

```

$ iverilog -o tb tb.v

$ ./tb

VCD info: dumpfile

oscillator.vcd opened for

output.

time= 0, sortie=x

time= 5, sortie=0

time= 10, sortie=1

time= 20, sortie=0

time= 30, sortie=1

time= 40, sortie=0

```

### Attention

- □ le bloc initial begin ... end n'est pas synthétisable!

- ⇒il doit être uniquement utilisé dans un «banc test».

- □ les temps d'attentes #5 indique d'attendre 5ns: ils ne sont **pas synthétisables**!

- ⇒il doit être uniquement utilisé dans un «banc test»

- □ le bloc forever #5 n'est pas synthétisable!

- ⇒il doit être uniquement utilisé dans un «banc test».

### Définition de constantes

```

localparam coeff = 5;

reg [31:0] x;

reg [31:0] y;

always @(*) begin

x = coeff * y;

end

```

- □ parameter: défini un paramètre global;

- □ localparam: défini un paramètre local au module.

### Module paramètrable

On peut définir un module paramétrable :

```

module circuit #(parameter taille=32)

(input [taille-1:0] entree,

output [taille-1:0] sortie);

sortie = ~a;

endmodule

module top_level();

localparam circuit1_taille = 64;

localparam circuit2_taille = 32;

reg [circuit1_taille-1:0] e1;

reg [circuit2_taille-1:0] e2;

wire [circuit2_taille-1:0] s1;

wire [circuit2_taille-1:0] s2;

circuit #(.taille(circuit1_taille)) circuit1 (.entree(e1), .sortie(s1));

circuit #(.taille(circuit2_taille)) circuit2 (.entree(e2), .sortie(s2));

endmodule

```

### Choix d'un «reg» ou d'un «wire»?

### Comment choisir entre «reg» et «wire»?

- - ⇒ il doit être déclaré comme un «registre» ;

Un **continuous assignment** est une affectation «combinatoire» où dès que la partie droite de l'affectation change, elle est prise en compte par la partie gauche de l'affectation:

```

wire a, b, c;

assign a = b & c;

```

Dès que b ou c change de valeur, l'expression b & c est évaluée et a est mis à jour avec le résultat. Dans le FPGA, il est probable qu'il sera simulé par une ou plusieurs LUTs.

> par défaut les entrées et sortie d'un module sont des «wires»

**mais** si un port de sortie doit être affecté dans un bloc «*always*», alors il doit être déclaré explicitement comme un registre :

```

module circuit (output reg sortie);

```

Et si on voulez faciliter l'accès à des données?

La mémoire 69

On peut définir des registres indexables :

```

reg [M:0] mémoire [N:0]

```

Ce qui définit:

- □ un tableau de N+1 éléments;

- ▷ où chaque élément est constitué de M+1 bits.

```

reg [31:0] memoire [7:0]; // définit un tableau de 8 valeurs sur 32bits

memoire[2] // le troisième élément du tableau

memoire[5][7:0] // l'octet de poids faible du sixième élément du tableau

```

Ce code donnera lieu à l'utilisation de la mémoire présente dans le FPGA, appelée BRAM.

La quantité de mémoire disponible dans un FPGA est indiquée en bits et cette mémoire peut être regroupée suivant des mots du nombre de bits voulu.

Par exemple, le ice40 hx8k propose 80kb de BRAM, soit 10ko de mémoire maximum.

Pour *«inférer»* par le synthétiseur de la mémoire BRAM, c-à-d de la mémoire interne au FPGA, il faut définir un module qui possède une *«interface»* propre à l'accès à la mémoire en lecture comme en écriture :

Le module de mémoire :

Pour utiliser le module mémoire :

```

module memoire #(

parameter WORD = 8,

parameter TAILLE = 10

(input clock,

input w en,

input r_en,

input [TAILLE_ADRESSE - 1:0] w_addr,

input [TAILLE_ADRESSE - 1:0] r_addr,

input [WORD - 1:0] w_data,

output reg [WORD - 1:0] r data

);

localparam TAILLE ADRESSE = $clog2(TAILLE);

reg [WORD - 1:0] mem [0:TAILLE - 1];

always @(posedge clock) begin

if (w en == 1'b1) begin

mem[w addr] <= w data;</pre>

end

if (r en == 1'b1) begin

r_data <= mem[r_addr];

end

end

endmodule

```

```

module led_sequencer(

input clock,

input slow_clock,

input reset,

output reg [3:0] LEDS);

reg w_en = 0;

reg r en = 1;

reg [3:0] r_addr;

reg [3:0] w addr = 0;

reg [7:0] w_data;

wire [7:0] r_data;

memoire #(.WORD(8), .TAILLE(10))

config leds

.clock(clock),

.w_en(w_en),

.r en(r en),

.w addr(w addr),

.r_addr(r_addr),

.w_data(w_data),

.r_data(r_data)

);

reg [3:0] adresse lecture = 0;

```

Il est possible que l'outil de synthèse simule de la mémoire avec des registres (read/write) ou des LUTs (read only).

### Inférence par l'outil de synthèse de l'utilisation de mémoire

```

xterm

yosys -ql synthese.log -p 'synth_ice40 -top top_level -json synthese.json' synthese.v

nextpnr-ice40 --freq 90 --hx8k --package tq144:4k --asc synthese.asc --pcf blackice-ii.pcf --json

synthese. json

Info: Packing constants...

Info: Packing IOs ..

Info: Packing LUT-FFs..

Info:

26 LCs used as LUT4 only

Info:

41 LCs used as LUT4 and DFF

Info: Packing non-LUT FFs..

22 LCs used as DFF only

Info: Packing carries..

Info:

0 LCs used as CARRY only

Info: Packing indirect carry+LUT pairs...

O LUTs merged into carry LCs

Info:

Info: Packing RAMs..

Info: Placing PLLs..

Info: Packing special functions..

Info: Packing PLLs..

Info: Promoting globals..

Info: promoting clock$SB_IO_IN (fanout 65)

Info: promoting reset_SB_LUT4_I3_3_O [reset] (fanout 24)

Info: Constraining chains...

2 LCs used to legalise carry chains.

Info:

Info: Checksum: 0x7d34fe38

Yosys a utilisé de la mémoire!

Info: Device utilisation:

Info:

ICESTORM LC:

93/ 7680

1%

Info:

38

ICESTORM RAM:

32

Info:

SB IO:

8/ 256

3%

2.5%

Info:

SB GB:

Info:

ICESTORM PLL:

0/

0 %

SB WARMBOOT:

1

08

Info:

```

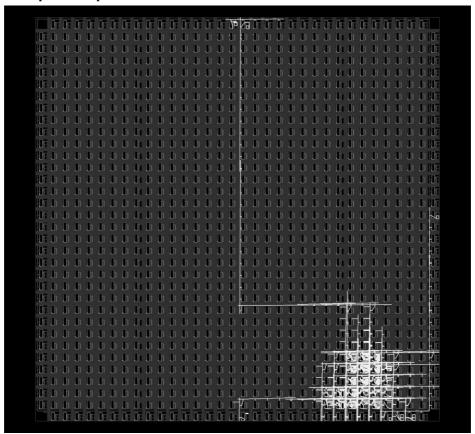

### Le placement réalisé par nextpnr

FPGA et «soft core» - P-FB

```

`include "fichier.v"

`ifndef CONSTANTES

`define CONSTANTES

`define NOMBRE_BITS 32

`endif

```

#### **Fonctions utiles**

| \$clog2(x) | retourne la valeur arrondie à la valeur supérieure de $log_2(x)$ |

|------------|------------------------------------------------------------------|

| \$floor(x) | arrondi à la valeur inférieure                                   |

| \$ceil(x)  | arrondi à la valeur supérieure                                   |

#### Exemple:

un compteur allant jusqu'à la valeur 500 000

```

reg [$clog2(500000):0] compteur;

```

Si on veut tester dans le simulateur «iverilog»:

```

module sortie_verilog;

initial

begin

$display("log2(500000)");

$display($clog2(500000));

$finish;

end

endmodule

```

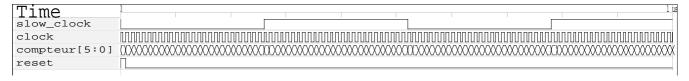

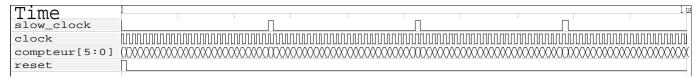

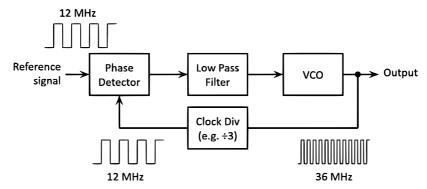

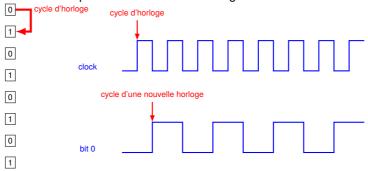

# Un diviseur d'horloge paramétrable

On peut l'utiliser comme «clock» d'un circuit séquentiel, c-à-d que l'horloge de ce circuit est différente des autres.

```

`timescale 1ns / 1ps

// HORLOGE_ENTREE 100_000_000

// HORLOGE SORTIE 4

// COMPTEUR =HORLOGE_ENTREE/HORLOGE_SORTIE = 25000000

//`define COMPTEUR 25000000

define COMPTEUR 25

module clock_divider(input clock, output reg slow_clock, input reset);

//parameter COMPTEUR = 25000000;

parameter COMPTEUR = 25;

reg [$clog2(COMPTEUR):0] compteur;

always @(posedge clock) begin

if (reset) begin

compteur <= 0;

slow clock <= 0;

end

else begin

compteur <= compteur + 1;</pre>

if (compteur == COMPTEUR) begin

compteur <= 0;

slow_clock <= ~ slow_clock;</pre>

end

end

end

endmodule

```

Mais attention : on passe d'un domaine d'horloge à un autre, ce qui peut être dangereux...

# Un générateur d'impulsion cyclique pramétrable

Cette solution est préférable car elle n'est pas utilisée pour piloter un circuit mais simplement comme référence :

```

`ifndef VALEURCOMPTEUR

`define HORLOGE_ENTREE 100000000

`define HORLOGE_SORTIE 16

`define VALEURCOMPTEUR (`HORLOGE_ENTREE/`HORLOGE_SORTIE)

endif

module clock_divider(input clock, output reg slow_clock, input reset);

localparam COMPTEUR = `VALEURCOMPTEUR;

reg [$clog2(COMPTEUR+1):0] compteur = 0;

always @(posedge clock) begin

if (reset) begin

compteur <= 0;

slow_clock <= 0;</pre>

end

else begin

if (compteur == COMPTEUR) begin

compteur <= 0;

slow clock <= 1;

end

else begin

compteur <= compteur + 1;</pre>

slow_clock <= 0;</pre>

end

end

end

endmodule

```

On appelle cette version «clock enabled» car dans le circuit séquentiel l'utilisant :

```

always @(posedge clock or posedge reset) begin

...

if (slow_clock) begin

// traitement lié à l'horloge dérivée

end

end

```

# Diviseur d'horloge

# Clock enabled ⇒ impulsion régulière

# Comment faire des circuits plus complexes? ⇒les FSMs!

Gestion des boutons 78

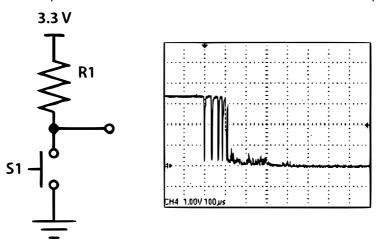

#### **Debouncing**

Lorsque l'on appui sur un **bouton mécanique**, la partie réalisant le contact électrique peut rebondir, «bounce», ce qui ouvre et ferme le circuit très rapidement : oscillation observée sur la trace d'oscilloscope

Ici, le bouton est «active low»:

- □ lorsqu'il est appuyé il met le signal à zéro;

- □ lorsqu'il est relâché, la résistance «pull-up» mets le signal à un.

#### Circuit réalisant le debouncing

- $\triangleright$  attendre au-dessus de 20 40ms;

- ⇒ si le bouton est encore appuyé : valider son appui.

L'appui du bouton est également **asynchrone** et il peut être nécessaire de le **synchroniser** au reste du circuit.

Un automate à nombre fini d'états est composé de :

□ états: ici, 3 états;

transitions: un événement;

⋄ incrémenter le compteur

envoyer une pulsation sur la sortie

#### En FPGA:

- logique séquentielle, pour «parcourir» l'automate en fonction de l'horloge;

- **registre** pour mémoriser un état: la taille du registre est proportionnelle au nombre d'états ( $log_2$ );

- les actions: modifier les valeurs de registres externes à l'automate;

- les transitions: évaluer des conditions :

- faire évoluer le registre d'état;

- ⇒un «case» en verilog

⇒ne pas oublier le cas «default» si on énumére pas toutes les valeurs possibles des états

compte tenu de la taille du registre d'état

(exemple 10 transitions parmis les 16 possibles d'un registre sur 4bits).

# FSM: le debouncing

```

pour les 100MHz du FPGA

ifndef HORLOGE

define HORLOGE 100000000.

endif

define NOMBRE ETATS 3

define MAXVALUE (`HORLOGE*40/1000)

module debouncer

input clock,

input reset,

input bouton,

output reg sortie);

reg [$clog2(`NOMBRE_ETATS)-1:0] etat;

reg [$clog2(`MAXVALUE+1):0] compteur;

localparam DEBUT = 0; - les états

localparam ATTENTE = 1;

localparam FIN = 2;

```

- ▷ lors du reset, on initialise l'automate à l'état de début ;

- ▶ les différentes actions sont exprimées dans le case;

- ▷ les transitions sont effectuées lors d'événements :

- passer de l'état DEBUT vers ATTENTE lors de l'appui du bouton;

- de l'état ATTENTE vers FIN lorsque le compteur est terminé;

```

always @(posedge clock or posedge reset) begin

if (reset) begin

etat <= DEBUT;</pre>

compteur <= 0;

end

else begin

case (etat)

DEBUT: begin

compteur <= 0;

sortie <= 0;

if (bouton) begin

etat<= ATTENTE;</pre>

end

end

ATTENTE: begin

compteur <= compteur + 1;</pre>

if (compteur >= `MAXVALUE)

etat <= FIN:

end

FIN:

if (bouton) begin

sortie <= 1;

etat <= DEBUT;

end

else

etat <= DEBUT;</pre>

default:

etat <= DEBUT;

endcase

end

end

endmodule

```

Dans l'état FIN, on mets la sortie à 1, puis on transite vers l'état DEBUT où la sortie repasse à zéro ⇒Une pulsation est transmise sur la sortie.

# FSM: le debouncing

```

define HORLOGE 1000

`include "debouncer.v"

`timescale 1ns / 1ps

module tb (); ---- le circuit de «test bench» ou «banc test»

reg clock;

reg reset;

rea bouton;

wire sortie;

- instanciation du module et connexion

debouncer dut (__--

.clock(clock),

.reset (reset),

.bouton (bouton),

.sortie(sortie)

initial begin _ - - - condition de départ

bouton = 0;

end

initial begin _ _ - - génération de l'horloge

clock = 1;

forever #5 clock = ~clock;

end

```

```

initial begin _ - - - envoi du reset

reset = 1;

#10 \text{ reset} = 0;

end

initial begin

$monitor("time %3d bouton %b sortie %b\n",

$time, bouton, sortie);

$dumpfile("debouncer.vcd");

$dumpvars(0, tb);

#22 bouton = 1; ---- création des événements

#8 bouton = 0:

#10 bouton = 1:

#543 bouton = 0;

#1000 $finish; ---- terminaison

end

endmodule

```

- ▷ \$monitor: affiche les contenus des signaux à chaque modification;

- ightharpoonup \$dumpfile et \$dumpvar: enregistre un fichier au format gtkwave

Mais un bouton, c'est pas de l'asynchrone?

# FPGA et «soft core» – P-FB

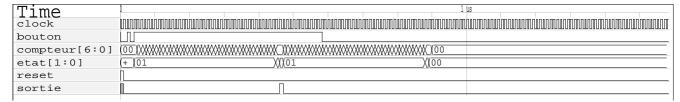

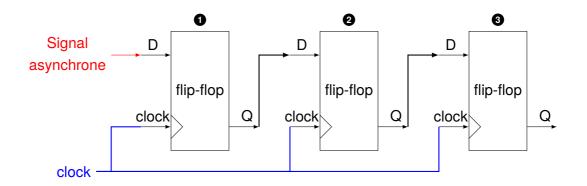

## Comment détecter un événement asynchrone dans un circuit FPGA synchrone?

Le «signal asynchrone» est en entrée de la flip-flop 1:

- ▷ le signal va probablement se modifier pendant le «time to setup» ou «time to hold» de la flip-flop;

- ⇒le signal va la mettre en «metastability»

- ⇒il va falloir un délai inconnu avant que la flip-flop atteigne un état stable.

- ⇒la sortie de **0** va finalement être synchronisée sur l'horloge;

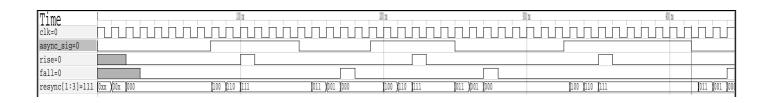

Pour détecter la transition, «edge», montante ou descendante, on compare les sorties de 2 et 3:

- > si elles sont différentes: une transition est détectée;

- suivant les valeurs de 2 et 3 on sait si elle est montante ou descendante.

```

xterm -

$ ./edge tb

time 0 async 0, fall x, rise x

time 20 async 0, fall 0, rise x

time 30 async 0, fall 0, rise 0

time 79 async 1, fall 0, rise 0

time 100 async 1, fall 1, rise 0

time 110 async 1, fall 0, rise 0

time 141 async 0, fall 0, rise 0

time 170 async 0, fall 0, rise 1

time 180 async 0, fall 0, rise 0

time 191 async 1, fall 0, rise 0

time 220 async 1, fall 1, rise 0

time 230 async 1, fall 0, rise 0

time 250 async 0, fall 0, rise 0

time 270 async 0, fall 0, rise 1

time 280 async 0, fall 0, rise 0

```

```

timescale 1ns / 1ps

//----TB---

module edge tb;

reg clk, async = 0;

wire rise, fall;

edge detect dut

(.async sig(async),

.clk(clk),

.rise(rise),

.fall(fall));

initial begin

clk = 1'b1;

forever #5 clk = ~clk;

end

// Produce a randomly-changing async signal.

time delav:

initial

begin

$dumpfile("edge tb.vcd");

$dumpvars(0, edge_tb);

$monitor("time %3d async %b, fall %b, rise

%b",

$time, async, rise, fall);

while ($time < 1000) begin

// wait for a random number of ns

delay = $urandom_range(50,100);

#delav:

async = \sim async;

génération de signal aléatoire

end

$finish:

end

```

endmodule

Le signal en entrée change de manière aléatoire dans le simulateur :

- ⇒ ses changements de valeur ne sont **pas synchronisés** sur l'horloge du circuit :

Pour chaque évévement au bord, «edge», c-à-d lorsque le signal asynchrone change :

- ⇒une **impulsion** est créée par le circuit.

Et comment on arrive à un circuit physique?

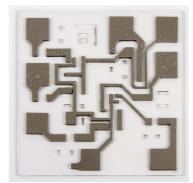

# Placement et Routage: réalisation du circuit dans le FPGA

- ▷ on réalise les fonctions logiques avec des (LUT) et les mémorisations de bits avec des Flip-Flops :

- ♦ sélectionner les blocks logiques qui vont les «héberger» ⇒ placement

- $\triangleright$  on route les E/S du circuit (e1, e2, ..., s1, s2, ...) vers d'autres blocks ou des pins d'E/S  $\Longrightarrow$  routage

On a sélectionner quatre blocks, router les E/S externes et internes, l'horloge...

# Placement et routage

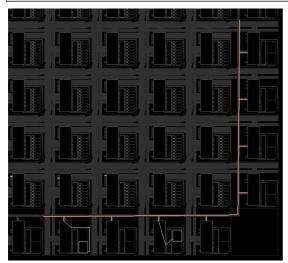

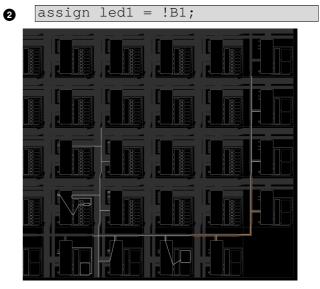

On réalise un simple circuit:

- un bouton est relié à une LED;

- la négation de l'état du bouton est reliée à la LED.

- assign led1 = B1;

Le routage connecte le «pad» d'entrée relié au bouton, au pad de sortie relié à la LED.

Le routage connecte le «pad» d'entrée relié au bouton à un block logique pour faire la négation, puis le résultat est relié au pad de sortie relié à la LED.

Les représentations données ont été obtenues grâce à l'outil «open source» nextpnr-ice40.

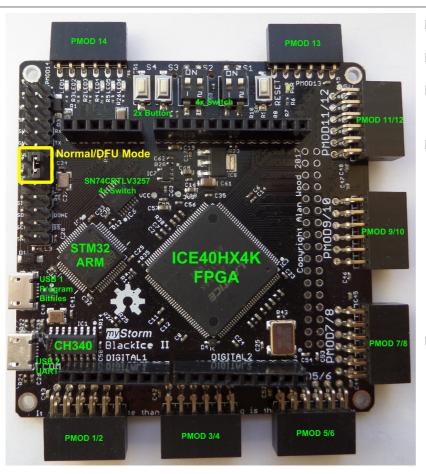

- □ contient un FGPA Lattice iCE 40HX8k;

- contient un micro contrôleur ARM STM32.

- ☐ le composant CH340 assure le lien USB-Serial;

- le microcontrôleur ARM STM32 assure la gestion du «bitstream» pour le FPGA:

- sauvegarde en mémoire flash pour programmation à l'allumage;

- transfert par le port série du bitstream pour programmation à la volée.

- des connecteurs standardisés au format PMODs.

Le «Black Ice II»

| □ Lattice Ice40 HX4K TQFP144 FPGA with 56 PIO and 80Kb BRAM & 4Mb (256kx16) SRAM |

|----------------------------------------------------------------------------------|

| □ STM32L433 ARM Cortex M4 Microcontroller 26 GPIO 256KB Flash and 64KB RAM       |

| □ 100Mhz Oscillator (Ice40), 12Mhz crystal (STM32)                               |

| □ SPI Mux control between Microcontroller, LEDs and RPi header                   |

| □ SDCard SDIO connections to both Ice40 and STM32L433                            |

| □ USB 1 - IceBoot for programming Ice40 with synthesised bitfiles                |

| □ USB 2 - Serial for monitoring and debugging Ice40 FPGA development             |

| □ Dip switches for input codes and/or configurations                             |

| □ Push Buttons for reading inputs and resetting the board                        |

| □ 4 x coloured LEDs for FPGA output indicators and fun!                          |

| □ 1 x Status LED, Programmed LED & a Power LED                                   |

| □ 6 x Double PMODS (8 PIOs each) expansion connectors                            |

| □ 2 x Single PMODS (4 PIOs each) extension connectors                            |

| ☐ Arduino Shield Compatible Headers (plus 4 pin extension)                       |

| ☐ RPi Header (26Pin) allows direct integration with all Raspberry Pi variants    |

| □ All hardware is Completely OpenSource and fully reusable                       |

| □ OpenSource Verilog Toolchain - Clifford Wolf's IceStorm                        |

| □ IceStudio and APIO support for getting started quickly                         |

- ⊳ FPGA iCE40 HX Family 3520 Cells 40nm Technology 1.2V

| Max Frequency                  | 533 MHz |

|--------------------------------|---------|

| Max Operating Temperature      | 85 °C   |

| Max Supply Voltage             | 1.26 V  |

| Memory Size                    | 10 kB   |

| Min Operating Temperature      | -40 °C  |

| Min Supply Voltage             | 1.14 V  |

| Number of Gates                | 3520    |

| Number of I/Os                 | 107     |

| Number of Logic Blocks (LABs)  | 440     |

| Number of Logic Elements/Cells | 3520    |

| Number of Macrocells           | 3520    |

| Number of Registers            | 3520    |

| Operating Supply Voltage       | 1.2 V   |

| RAM Size                       | 10 kB   |

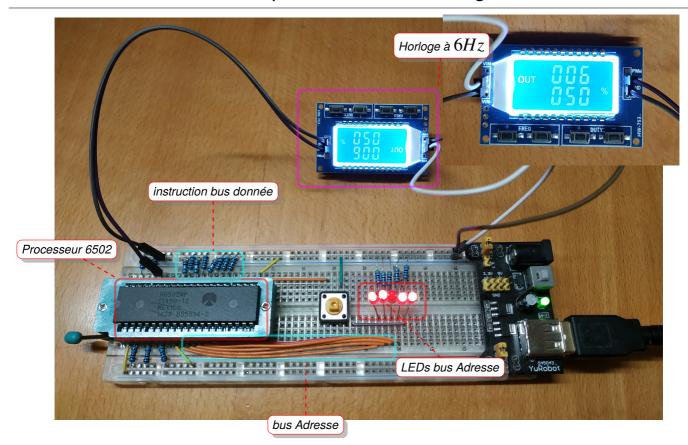

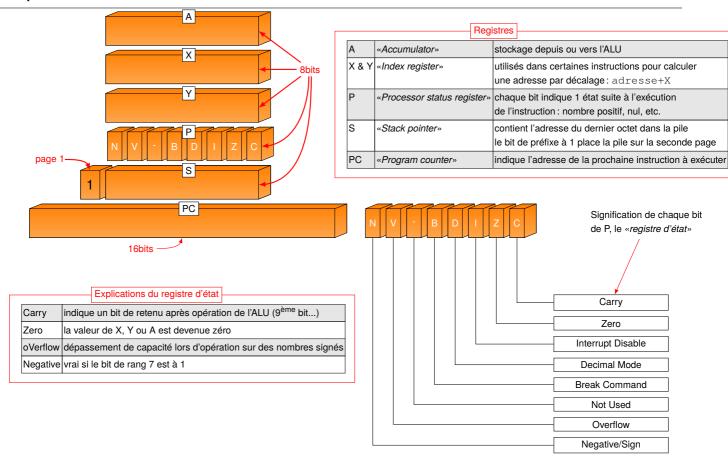

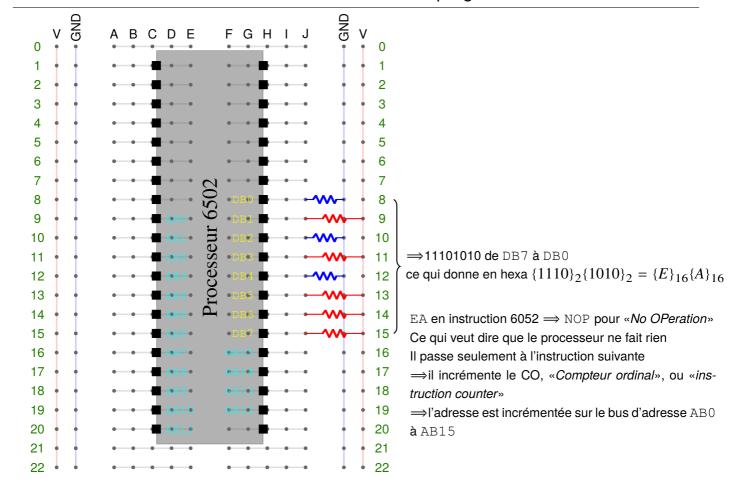

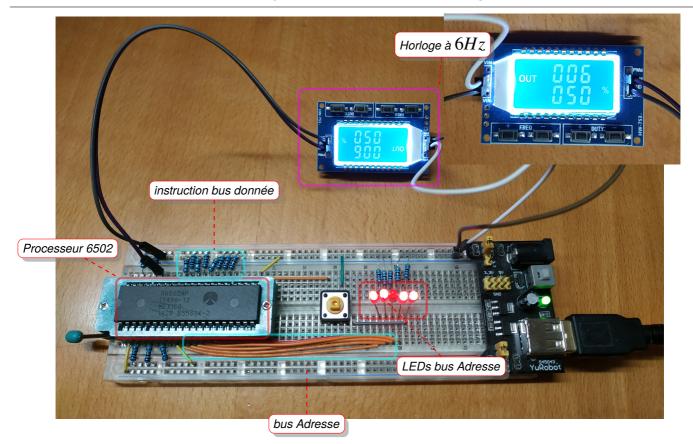

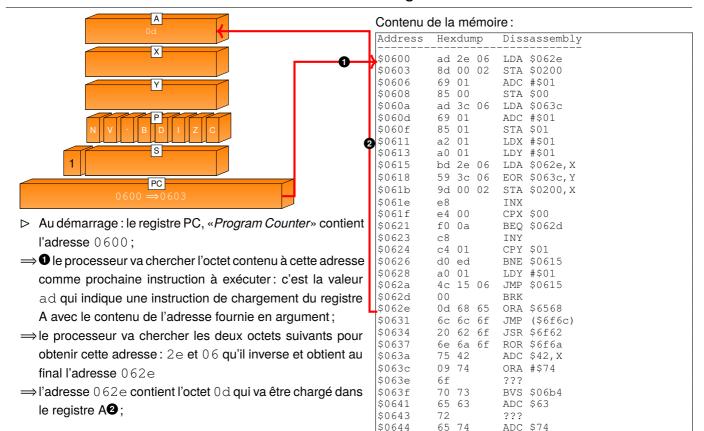

# Mais ça marche comment un processeur? exemple le processeur 6502

# Processeur 6502

- □ processeur développé par Chuck Peddle pour la société MOS Technology;

- □ introduit en 1975;

- □ très populaire:

Apple IIe

Commodore PET

**BBC Micro**

Atari 2600

Atari 800

Commodore VIC-20

Family Computer

Ohio Scientific Challenger 4P

Tamagotchi digital pet<sup>[53]</sup>

Atari Lynx

- □ toujours en vente et utilisé dans les systèmes embarqués;

- □ processeur 8bits, avec un bus d'adresse sur 16bits et «little-endian», cadencé de 1 à 2 MHz

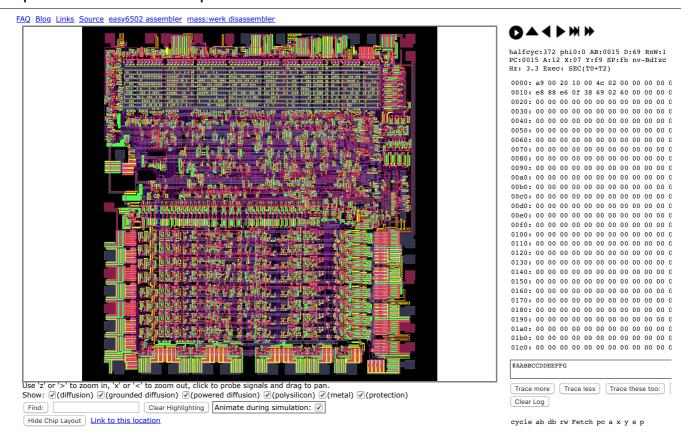

http://www.visual6502.org/JSSim/expert.html

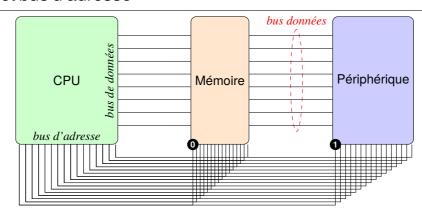

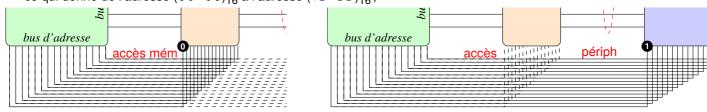

#### Pour accéder à:

#### ▷ la mémoire :

- on va de l'adresse (0000 0000 0000 0000), à l'adresse (0111 1111 1111 1111);

- $\diamond$  ce qui donne de l'adresse (00 00)<sub>16</sub> à l'adresse (7F FF)<sub>16</sub>;

#### aux périphériques:

- on va de l'adresse (1000 0000 0000 0000)<sub>2</sub> à l'adresse (1111 1111 1111 1111)<sub>2</sub>;

- ♦ ce qui donne de l'adresse (80 00)<sub>16</sub> à l'adresse (FF FF)<sub>16</sub>;

- - $\Box A_0, ..., A_{15}$ : 16 bits d'adresse;

- $\square$   $D_0, ..., D_7$ : 8 bits de données;

- $\square$  R/W: indique si c'est une opération de lecture ou d'écriture ;

- > Interactions avec l'extérieur :

- $\Box$  *Sync*: signal d'horloge: ryhtme le travail du processeur;

- □ *NMI*: «*Non Maskable Interruption*»: signal d'interruption;

- □ *RES*: «*reset*», réinitialise l'état du processeur et, si maintenue, le bloque;

Et la programmation d'un processeur?

| Ω          |

|------------|

| P-FI       |

|            |

| Ω.         |

| -1         |

| ^          |

| core»      |

| `≤         |

| Ņ          |

| O          |

| soft core  |

| Ö          |

| ŏ          |

| v          |

| ı.         |

| eţ         |

|            |

| ⋖          |

| FPGA       |

| $\tilde{}$ |

| -          |

|            |

| mode      | opérande                                                                     |

|-----------|------------------------------------------------------------------------------|

| immédiat  | la donnée                                                                    |

| absolu    | n'importe quelle adresse                                                     |

| page zéro | un octet correspondant au second octet d'adresse, le premier est fixé à zéro |

| indexé X  | adresse+registre X                                                           |

| indexé Y  | adresse+registre Y                                                           |

| implicite | pas d'opérande                                                               |

| relatif   | un octet relatif en complément à deux, de -128 à 127                         |

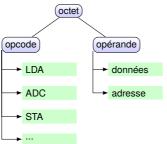

Chaque instruction est codée sur un octet en fonction du mode choisi.

Exemple: l'instruction ADC donne l'octet 69 si la valeur à additionner est donnée en paramètre (mode immédiat).

69 01 signifie additionner la valeur 1 dans l'accumulateur.

Certaines instructions **modifient le registre d'état P**: Exemple pour faire un saut sur la condition que X soit égal à zéro:

CPX \$0; compare la valeur du registre X avec  $0 \Longrightarrow$  positionne le bit Z à nul si les deux valeurs sont identiques (on fait une soustraction)

${\it BEQ}$  0A; test la valeur du bit Z: 1 donne vrai et 0 donne faux

Un octet en mémoire peut être :

| Ins | description                                               | mode adressage |        |            |          |          |           |         |

|-----|-----------------------------------------------------------|----------------|--------|------------|----------|----------|-----------|---------|

|     |                                                           | immédiat       | absolu | page zéro  | indexé X | indexé Y | implicite | relatif |

| ADC | ajoute un octet avec le bit de retenu dans l'accumulateur | 69             | 6D     | 65         | 7D       | 79       |           |         |

| BEQ | «Branch if EQual», saut vers une adresse si vrai          |                |        |            |          |          |           | F0      |

| BNE | «Branch if Not Equal», saut vers une adresse si faux      |                |        |            |          |          |           | D0      |

| CPX | compare avec le registre X                                | E0             | EC     | E4         |          |          |           |         |

| INX | Incrémente la valeur dans le registre X                   |                |        |            |          |          | E8        |         |

| INY | Incrémente la valeur dans le registre Y                   |                |        |            |          |          | C8        |         |

| JMP | «JuMP», saut                                              |                | 4C     |            |          |          |           |         |

| JSR | «Jump to SubRoutine», saut vers<br>un sous-programme      |                | 20     |            |          |          |           |         |

| LDA | charge un octet dans le registre A                        | <b>A</b> 9     | AD     | <b>A</b> 5 | BD       | В9       |           |         |

| LDX | charge un octet dans le registre X                        | A2             | ΑE     | A6         |          | BE       |           |         |

| LDY | charge un octet dans le registre Y                        | Α0             | AC     | Α4         | вс       |          |           |         |

| RTS | «ReTurn from Subroutine», retour d'un sous-programme      |                |        |            |          |          | 60        |         |

| STA | stocke l'accumulateur à une<br>adresse donnée             |                | 8D     | 85         | 9D       | 99       |           |         |

| NOP | ne fait rien                                              |                |        |            |          |          | EΑ        |         |

Et pour des programmes plus gros?

104

#### Sur 8bits

adresse1 + adresse2 adresse3

#### Le programme assembleur :

| LDA adresse1 | ; charge le nombre stocké à l'adresse 1 dans l'accumulateur  |

|--------------|--------------------------------------------------------------|

| ADC adresse2 | ; additionne le nombre stocké à l'adresse 2 à l'accumulateur |

| STA adresse3 | ; stocke le contenu de l'accumulateur à l'adresse 3          |

| RTS          | ; retourne                                                   |

#### Les mnémoniques:

| AD | adresse1 |

|----|----------|

| 6D | adresse2 |

| 8D | adresse3 |

| 60 |          |

#### Sur 16bits

Le premier nombre sur deux octets W W1

Le second nombre sur deux octets X X1

Attention: on est en «Little Endian»,

c-à-d avec inversion des octets de la valeur sur 16bits.

|                |     | oc              | tets            |                   |

|----------------|-----|-----------------|-----------------|-------------------|

|                |     | 1 <sup>er</sup> | 2 <sup>nd</sup> |                   |

| Premier nombre | 307 | 51              | 1               | car 307=1*256+51  |

| Second nombre  | 764 | 252             | 2               | car 764=2*256+252 |

#### Le programme assembleur :

| CLC |         |    |

|-----|---------|----|

|     | adresse |    |

| ADC | adresse | X  |

|     | adresse |    |

| LDA | adresse | W1 |

|     | adresse |    |

| STA | adresse | Y1 |

| LDA |         |    |

| ADC |         |    |

|     | adresse | Z  |

| RTS |         |    |

## ⇒ on utilise le bit de retenu...

#### Les mnémoniques:

| 18 |         |    |  |

|----|---------|----|--|

| AD | adresse | W  |  |

| 6D | adresse | X  |  |

| 8D | adresse | Y  |  |

| AD | adresse | W1 |  |

| 6D | adresse | X1 |  |

| 8D | adresse | Y1 |  |

| Α9 | 00      |    |  |

| 69 | 00      |    |  |

| 8D | adresse | Z  |  |

| 60 |         |    |  |

|    | · ·     | ·  |  |

FPGA et «soft core» – P-FB

# Programmation du 6502 en assembleur

## Application d'un xor d'un texte avec un mot de passe

Le programme calcule  $saisie_i \oplus mdp_i$  pour chaque caractère i de saisie et de mdp.

```

1 define sortie $200 ; on définie l'adresse de sortie à 0200

; on lit la taille de la chaîne saisie

3 LDA saisie

4 STA sortie

; on la reporte dans la chaîne de sortie

; on incrémente la valeur pour la comparaison utilisée pour arrêter la boucle

5 ADC #$1

6 STA $0

; on la stocke dans la page zéro

; on lit la taille de la chaîne mdp

7 LDA mdp

; on incrémente la valeur utilisée pour réinitialiser l'utilisation du mdp

8 ADC #$1

9 STA $1

; on la stocke dans la page zéro

11 LDX #$1

; on charge la valeur 1 dans le registre X

12 LDY #$1

; on charge la valeur 1 dans le registre Y

14 boucle:

; on définit une étiquette

LDA saisie, X ; on charge dans l'accumulateur la valeur à l'adresse saisie+X

EOR mdp, Y

; on réalise un xor entre le registre A et la valeur à l'adresse mdp+Y

; on stocke le résultat à l'adresse sortie+X

STA sortie, X

INX

: on incrémente la valeur contenu dans le registre X

CPX $0

; on compare la valeur de la taille de la chaîne saisie

20

BEO fin

; si elle est identique, on a fini et on mets l'adresse fin dans le registre PC

21

; on incrémente la valeur contenue dans le registre Y

INY

CPY $1

; on compare avec la valeur de la taille de la chaîne mdp

; si elle n'est pas égale on recommence la boucle en sautant à l'adresse boucle

BNE boucle

; sinon on réinitialise le registre Y à 1

LDY #$1

; et on effectue un saut à l'adresse boucle

JMP boucle

26 fin:

; étiquette

27

; instruction d'arrêt

BRK

28

29 saisie:

dcb 5,$68,$65,$6c,$6c,$6f ;hello

31 mdp:

dcb $9,$74,$6f,$70,$73,$65,$63,$72,$65,$74;topsecret

```

| m             |

|---------------|

| ш             |

| P-FB          |

| ī             |

| core»         |

| $\mathcal{E}$ |

| oft           |

| t «soft       |

| ē             |

| ⋖             |

| FPGA et       |

| 芷             |

|               |

| Address | Hexdump |    |    | Diss | sassembly |

|---------|---------|----|----|------|-----------|

| \$0600  | ad      | 2e | 06 | LDA  | \$062e    |

| \$0603  | 8d      | 00 | 02 | STA  | \$0200    |

| \$0606  | 69      | 01 |    | ADC  | #\$01     |

| \$0608  | 85      | 00 |    | STA  | \$00      |

| \$060a  | ad      | Зс | 06 | LDA  | \$063c    |

| \$060d  | 69      | 01 |    | ADC  | #\$01     |

| \$060f  | 85      | 01 |    | STA  | \$01      |

| \$0611  | a2      | 01 |    | LDX  | #\$01     |

| \$0613  | a0      | 01 |    |      | #\$01     |

| \$0615  |         |    | 06 |      | \$062e,X  |

| \$0618  | 59      | Зс | 06 | EOR  | \$063c,Y  |

| \$061b  | 9d      | 00 | 02 | STA  | \$0200,X  |

| \$061e  | e8      |    |    | INX  | /         |

| \$061f  | e4      | 00 |    | CPX  | \$00      |

| \$0621  | f0      | 0a |    | BEQ  | \$062d    |

| \$0623  | с8      |    |    | INY  |           |

| \$0624  | С4      | 01 |    |      | \$01      |

| \$0626  | d0      | ed |    |      | \$0615    |

| \$0628  | a0      | 01 |    |      | #\$01     |

| \$062a  | 4c      | 15 | 06 | JMP  | , , ,     |

| \$062d  | 00      |    |    | BRK  | //        |

| \$062e  |         | 68 |    |      | \$6568    |

| \$0631  | 6с      | 6с |    |      | (\$6f6c)  |

| \$0634  | 20      | 62 | 6f |      | \$6f62    |

| \$0637  | 6e      | 6a | 6f | ROR  |           |

| \$063a  | 75      | 42 |    |      | \$42, X   |

| \$063c  | 09      | 74 |    | ORA  |           |

| \$063e  | 6f      |    |    | ???  |           |

| \$063f  | 70      |    |    | BVS  |           |

| \$0641  | 65      | 63 |    | ADC  |           |

| \$0643  | 72      |    |    | ???  | •         |

| \$0644  | 65      | 74 |    | ADC  | \$74      |

| 0600: | ad | 2e | 06  | 8d | 00 | 02 | 69 | 01 | 85 | 00 | ad | 3с | 06 | 69 | 01 | 85 |

|-------|----|----|-----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 0610: | 01 | a2 | 01  | a0 | 01 | bd | 2e | 06 | 59 | Зс | 06 | 9d | 00 | 02 | e8 | e4 |

| 0620: | 00 | f0 | 0 a | с8 | С4 | 01 | d0 | ed | a0 | 01 | 4c | 15 | 06 | 00 | 0d | 68 |

| 0630: | 65 | 6c | 6с  | 6f | 20 | 62 | 6f | 6e | 6a | 6f | 75 | 72 | 09 | 74 | 6f | 70 |

| 0640: | 73 | 65 | 63  | 72 | 65 | 74 |    |    |    |    |    |    |    |    |    |    |

# On note que:

|   | \$062e | adresse de la chaîne saisie              |

|---|--------|------------------------------------------|

| / | \$063c | adresse de la chaîne mdp                 |

|   | \$062d | adresse de l'instruction brk             |

|   | \$062e | le désassembleur trouve des instructions |

|   |        | dans le contenu de la chaîne saisie      |

|   |        | ⇒ Interprétation automatique erronée     |

|   | \$063e | Interprétation automatique impossible,   |

|   | \$0643 | il n'y a pas d'instruction reconnue      |

⇒ le registre PC passe alors à 0603 pour exécuter la prochaine instruction.

L'exécution d'une instruction et l'accès mémoire prends plusieurs cycles d'horloge.

Et les processeurs plus modernes?

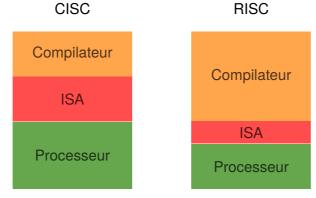

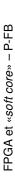

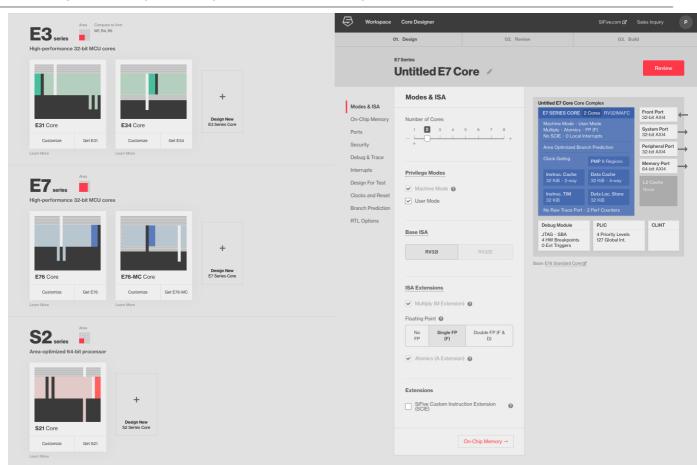

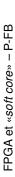

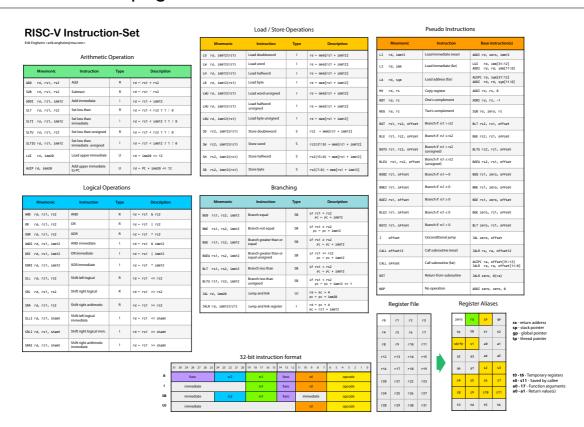

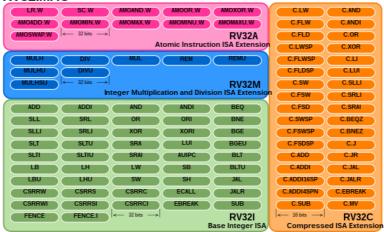

- □ «Open Standard Instruction Set», ISA;

- basé sur les principes RISC, «Reduced Instruction Set Computer»;

- □ licence «Open Source» sans royalties, mais des extensions payantes...;

- □ supporté par :

- différentes entreprises au niveau de l'offre hardware : sifive ;

- différents OS: Linux, FreeRTOS;

- différents «toolchains»: compilateur, linkeur, constructeur de firmware;

- sous formes de différentes «IPs» pour FPGA, «Field Programmable Gate Array».

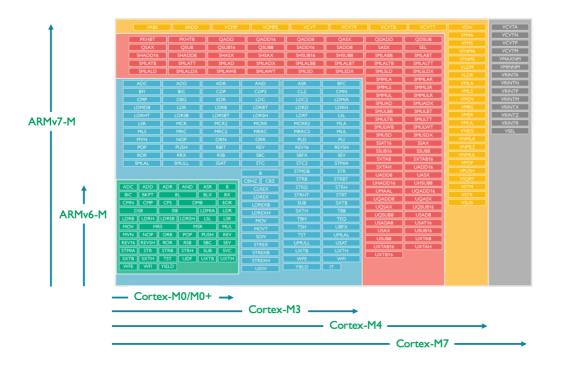

ARM Cortex et ISA

ARM Cortex et ISA

Floating Point

DSP (SIMD, fast MAC)

Advanced data processing bit field manipulations

General data processing I/O control tasks

Le Jeu d'instruction RISC-V

| Name      | Description                                                                                                      | Version | Status   | Instruction count |  |  |  |

|-----------|------------------------------------------------------------------------------------------------------------------|---------|----------|-------------------|--|--|--|

| Base      |                                                                                                                  |         |          |                   |  |  |  |

| RVWMO     | Weak Memory Ordering                                                                                             | 2.0     | Ratified |                   |  |  |  |

| RV32I     | "Base Integer Instruction Set 32-bit"                                                                            | 2.1     | Ratified | 49                |  |  |  |

| RV32E     | "Base Integer Instruction Set (embedded) 32-bit 16 registers"                                                    | 1.9     | Open     | 49                |  |  |  |

| RV64I     | "Base Integer Instruction Set 64-bit"                                                                            | 2.1     | Ratified | 14                |  |  |  |

| RV128I    | "Base Integer Instruction Set 128-bit"                                                                           | 1.7     | Open     | 14                |  |  |  |

| Extension |                                                                                                                  |         |          |                   |  |  |  |

| М         | Standard Extension for Integer Multiplication and Division                                                       | 2.0     | Ratified | 8                 |  |  |  |

| Α         | Standard Extension for Atomic Instructions Floating point operation                                              | 2.1     | Ratified | 11                |  |  |  |

| F         | Standard Extension for Single-Precision Floating-Point                                                           | 2.2     | Ratified | 25                |  |  |  |

| D         | Standard Extension for Double-Precision Floating-Point                                                           | 2.2     | Ratified | 25                |  |  |  |

| Zicsr     | Control and Status Register (CSR)                                                                                | 2.0     | Ratified |                   |  |  |  |

| Zifencei  | Instruction-Fetch Fence                                                                                          | 2.0     | Ratified |                   |  |  |  |

| G         | "Shorthand for the IMAFDZicsr Zifencei base and extensions intended to represent a standard general-purpose ISA" | N/A     | N/A      |                   |  |  |  |

| Q         | Standard Extension for Quad-Precision Floating-Point                                                             | 2.2     | Ratified | 27                |  |  |  |

| L         | Standard Extension for Decimal Floating-Point                                                                    | 0.0     | Open     |                   |  |  |  |

| С         | Standard Extension for Compressed Instructions                                                                   | 2.0     | Ratified | 36                |  |  |  |

| В         | Standard Extension for Bit Manipulation                                                                          | 0.93    | Open     | 42                |  |  |  |

| J         | Standard Extension for Dynamically Translated Languages                                                          | 0.0     | Open     |                   |  |  |  |

| Т         | Standard Extension for Transactional Memory                                                                      | 0.0     | Open     |                   |  |  |  |

| Р         | Standard Extension for Packed-SIMD Instructions                                                                  | 0.2     | Open     |                   |  |  |  |